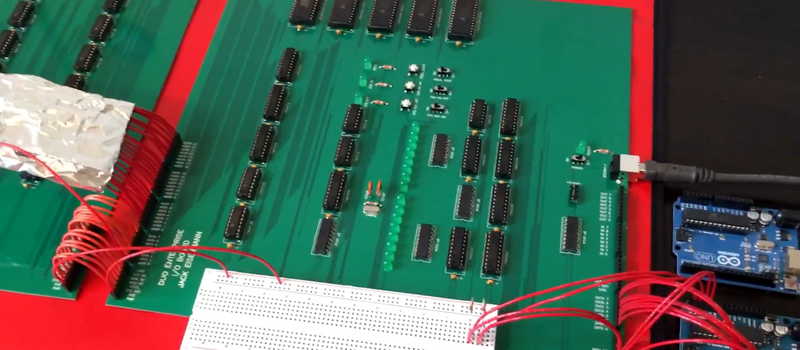

[Jack Eisenmann] is no stranger to building impressive DIY CPU’s on vast stretches of breadboard. This time [Jack] has done away with the seventeen breadboards he used in his last 8-bit computer and instead has gone a step further and designed a set of generously utilised PCB’s for the CPU. The result is the DUO Enterprise.

The CPU design is based around an 8-bit data bus and a 24-bit address bus. As usual, a minimal yet carefully chosen instruction set allows [Jack] to do all the heavy lifting in software as part of the compiler and operating system he is working on. There is no sign of a display yet, instead the computer communicates via a dumb terminal. We love the aluminum foil for shielding! Check out the video, below, to see what we mean.

Over the years, we have seen many of [Jack]’s other CPU builds featured on Hackaday. One of his first designs was a 4-bit CPU that could play many games on a LED matrix.Later he did a much more impressive 8-bit CPU along with analog video output and an OS ofcourse. It could even play pong. He even built a Single Instruction Set Computer (SISC).

His final goal with DUO Enterprise is to allow anyone to utilise its computing power by submitting programs and calculations. Heads up [Jack], our neural net needs training soon.

Wow, that looks great! What instruction set are you making for it?

I don’t think using your PC as a dumb terminal spoils anything. But using the Arduino’s as a loader is sort of cheating.

Are you planning to just use the Arduino to load the Flash, then talk to the system directly through a UART?

You can see the instruction set by following the link in the article above. It has 16 bit instructions that include an 8 bit constant. So it’s a Really Really Reduced Instructions Set Computer (RRRISC).

Having something like an Arduino as a boot loader doesn’t have to be permanent but it sure saves time when developing code.

Kewl and interesting project. It would make a good HDL tutorial.

Heh, I remember hearing of a museum that had an early piece of old iron, and at the time they were bootstrapping it off an 80s 8bit micro, because it was easier than standing there for an hour flipping switches.

From the white paper, it looks like there’s really only one instruction, a move source to destination instruction. The sources include arithmetic operations. They also include a constant embedded in every instruction. Destinations include the PC, so you can jump. And every instruction can be made unconditional or conditional on carry set, so you have conditional skips, branches, and execution.

The ISA seems like a transport-triggered architecture, like a lot of “one instruction” computers.

https://en.wikipedia.org/wiki/One_instruction_set_computer

In the article it mentions that [Jack Eisenmann] built a single instruction set computer (SISC). It looks like he has used a very similar feature here with the selective conditional on every instruction and that’s what makes this look *like* a Transport Triggered Architecture (TTA) but it’s not a TTA.

It’s even more like a scaled down Complex Instruction Set Computer (CISC) than a Reduced Instruction Set Computer (RISC) but calling it a RISC is more intuitive as it has a very small instruction set.

Here is why I say that –

A CISC has this sort of instruction set architecture –

xxxx xxxx xxxx xxxx bits

..|....|....|...|.|

..|....|....|...|..-- instruction modifier

..|....|....|....---- data destination

..|....|.....-------- data source

..|.....------------- logical opperation

...------------------ instruction groupings

So with a CISC you tend to have fixed bit fiels that encode the instruction.

Alternativel with RISC you have *varying* bit fields that encode instructions

0Maa abbb transfer register 'a' to register 'b' or if M to alternate 'b'

10aa abbb similar instruction one of 8 to one of 8

110a abbb 4 instructions with a 3 bit operand

1110 aabb 4 instructions with a 2 bit operand

1111 0xxx 8 ALU functions

1111 10ab 2 instructions with a 1 bit operand (like conditionals)

1111 1100 1 instruction with no operand

1111 1110 1 instruction with no operand

1111 1111 reset instruction

So it’s more like a scaled down CISC than a RISC

Why so huge PCB’s ?

#becauseHeCan

I love having the luxury of a huge PCB footprint to play around on to align parts in an interesting manner that’s easy to troubleshoot. I’m so used to designing for economies for scale, sometimes I forget to give myself a little extra breathing room on personal projects :) This guy seems to enjoy stretching his legs ( and traces! )

No… There comes a point when an excessive footprint just becomes a PITA. Not only for storage, But for enclosures too.

Most of the PCB real estate is taken up by routing the various buses to almost every chip. This is what happens inside a CPU but with a CPU we don’t see how much bus routing there is so we don’t think about it.

“We love the aluminum foil for shielding!”

And, yet, if I wear it on my head, all I get is mockery.

(c:

We meant to tell you, but we’d take it much more serious if you had a 0 gauge ground cable to copper plates on the soles of your shoes.

Given the brainwave frequency is between 0.5Hz to 42Hz, the shielding got to be a few skin depths for effective shielding the magnetic component too. :P

http://chemandy.com/calculators/skin-effect-calculator.htm

You’re the man, Jack!

Good to see you got another hackaday!