When we are introduced to the internals of a microprocessor, it is most likely that we will be shown something like one of the first generation of 8-bit CPUs from the 1970s. There will be the familiar group of registers and counters, an arithmetic and logic unit (ALU), and an instruction decoder with associated control logic. A complex instruction set causes the decoder to marshal registers and ALU to perform all the various functions in the right order. CPUs may have moved on in many ways since the 1970s, but the block diagram of an 8080 or similar still provides a basic grounding for the beginner.

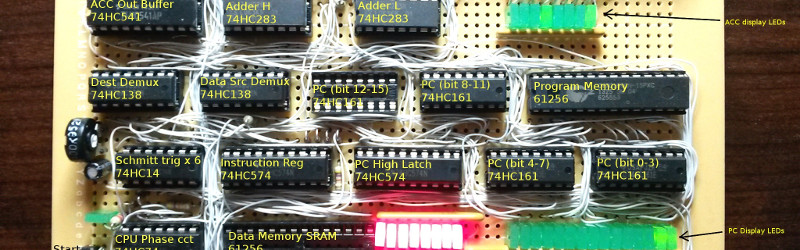

So when we tell you about another home-made CPU using TTL logic chips, you might expect it to follow this well-worn path. Fortunately though the hardware hacking community is always capable of springing surprises upon us, and [Szoftveres] has done just that with his design. It’s a one-instruction-set machine following a transport triggered architecture, and that means it deviates sharply from the conventional architecture described above. Each instruction is a move between the different physical functions of the processor, and computation is achieved by the physical functions working on the data as it is moved into them and presenting the result on their outputs ready to be moved elsewhere. The result is a computer that is in its own way beautifully simple, though at the expense of some inflexibility and lack of some hardware functions we take for granted in more conventional processors.

This machine has been built on a piece of stripboard, and has an accompanying board with display, keypad, and a modem. There is a small board based upon an ATmega8 microcontroller which performs the function of fast program loading, and can be removed once the code is loaded. Software can be written in a C-like language anc compiled using the compiler in his GitHub repository, and he has produced a YouTube video of the machine in operation. This project is well worth reading through in-depth, for its introduction to this slightly unusual architecture.

We have brought you numerous 74 TTL logic CPUs over the years, but surprisingly this one is not the first single-instruction design.

Wow. Yet another TTL CPU. Extra points for the bubble 7 segment display!!!

All the low fruit is gone now we have seen CISC, RISC, single instruction, Harvard, Von Newman and now a new level up with this Transport Triggered Architecture.

About the only thing we haven’t seen are pipelined (no point with TTL chips) and really odd architectures like the Propeller.

This one is really well thought out and documented. It’s also the most complete I have seen with a full custom compiler and tool chain. That must have been just as hard as making the hardware.

I think we have a winner lol.

One other thing … I used to call this board type “dot board” or perfboard. It doesn’t have stripes.

Is the Propeller really odd?

Each of the 8 (!odd(8)) cores covers maps the whole RAM to registers or the other way round. Some ppl say “executable registers” instead of “memory mapped registers”. Beyond this, the architecture of the cores looks very common.

The (Hub-)RAM which these cores can access is a shared external storage from the viewpoint of the cores. This may not be compared to the main RAM of other CPUs. Perhaps this is the biggest source of confusion?

The rest of the P8X32A is some on chip hardware (per core) like other MCUs have in far higher amounts. So even (== !odd) kind of less strange than others.

I like these beasts!

But: With round about 8€ per chip, you keep your Propellers together, give them individual names and use cheaper chips for the everyday tasks in MCU-land…

;-)

I have always found the Propeller to be a curious chip but I have never bothered to buy one. It would be a fun chip to code for but first I would have to learn yet another assembly. Yes, I know about SPIN.

The Propeller very much seems to be a solution to a problem that I have never come across. It’s like – if I need more multitasking or better ISR response times on a single core chip when I just get a faster chip and time divide processes.

A part of me wishes I had *that* problem that a Propeller solves just so I can buy one. So while it certainly seems like it would be a fun chip to play with, I cannot think of a single application that needs the extra complexity and features of a Propeller.

One day I will get to it.

All those types of computer that you mentioned are Von Neumann* machines at least normally. They could be Harvard machines (separate data and instruction space) and e.g. the TTA machine could use distributed storage with no common address space which would make it neither Von Neumann nor Harvard.

Pipelined TTL designs weren’t exactly uncommon BTW, it is more a problem of complexity, power and cost that limit homemade computers to non-pipelined designs. Besides compared to a modern computer even an aggressively pipelined TTL machine would be extremely slow limiting the attraction of spending more money and a lot of more time on it.

(* He didn’t invent the type (and never claimed he did) and didn’t limit himself to that kind of computers – but the name stuck)

There isn’t really a “normally”.

A PIC is both RISC and Harvard. Not that that matters if your starting from TTL because it can be what ever you want it to be.

A lot of AVR’s are a modified Harvard. Most of the older CISCs are Von Newman but not exclusively. Some have internal ROM and a separate external bus for RAM.

RÖB says: “About the only thing we haven’t seen are pipelined (no point with TTL chips)”

Ok, I’ll bite: https://hackaday.io/project/20781-breadboard-color-computer-from-ttl

A TTL CPU with a pipelined architecture to generate VGA from software at a reasonable resolution.

lol

Just awesome

All these homegrown CPUs and systems are lots of fun to look at and think about.

The ones with toolchain are an own level.

What would be next?

Homegrown⁴: Homegrown CPUs in homegrown systems which are running a homegrown OS containing their own homegrown toolchain?

“hg⁴”?

Four? Forth?

Forth probably does this already…

…are there other hg⁴ systems besides Forth?

Home grown CPUs certainly taught a lot more than one usually learns these days, unless they’re a compiler or embedded systems designer.

I actually do design simple embedded systems, and got my MS in computer engineering. I learned digital logic, how the 68k and MSP-430 worked at low levels and how to work with them, and how to integrate them into applications.

The gap between digital logic and microprocessors was never bridged, and I’ve spent the past 2 years fiddling with a homegrown CPU architecture to fill that void.

My manager studied electrical engineering in Columbia in the early 90’s, and every student had to build an 8-bit TTL CPU. I wish modern American universities provided that depth in their curriculum.

I don’t think this project is really a one instruction architecture. The inclusion of two bits in the instruction word to perform different functions really means this a four instruction architecture. Conditional branching can be done with one instruction but it’s a little more complicated. But still this is a great project.

Interesting. Both sources and sinks are encoded with 3 bits, allowing a maximum of 8 sources and 8 sinks on the internal bus. From the block diagram it appears there are 3 sources and 8 sinks. That looks like plenty of room to add sources for shifting and bitwise inversion (all operating on an existing register e.g. the accumulator output, to avoid adding sinks), but it’s cool to see how he implemented those in software instead, all in terms of addition (with carry feedback and if-zero flags).

Thanks for the terrific post. The work overall is very nice but i’m especially impressed by the nicely laid out compiler. I built my own compiler based on LCC. It was probably less work but yours is very easy to follow and learn from. I’m going to build it for fun and keep it in mind for the future.

HaD said: “…and really odd architectures like the Propeller.”

TL;DR: The Propeller is NOT “odd”. It is really useful when applied properly…

I say: There’s nothing “odd” about the Propeller! Maybe it seems “odd” to an relatively inexperienced Engineer. The concept of the Propeller is simple; a parallel clocked set of identical programmable state-machines with a common parallel deterministic commutated I/O bus. The architecture is defined, both mathematically, and proven in-practice. The Propeller may not be “like” your “usual” sequential-state device you see on a daily basis – but it certainly isn’t “odd”. Anyone can duplicate the Propeller using other processors in parallel with a supervisor part and commutating bus switches (imaging a fast CPLD commutating a bunch of bubble-gum microcontrollers). But keep in-mind, from a microcontroller-standpoint, the Propeller is no speed slouch.

I use the Propeller chip often when prototyping applications where the application needs parallel or parallel-like processing without the burden/overhead of a single-threaded interrupt-driven device which just gets in the way in the dev-phase.

In the end however, taking the Propeller design to production usually doesn’t work with the Propeller part, it’s just too expensive, and not second-sourced. (Small volume low-risk is OK though). Instead I map the propeller code to a single-threaded processor using case/and-or interrupt state branches. But the Propeller can be priceless in shortening the dev-time (and time is money).

The Propeller could have been the “Arduino” of sorts for the “Maker” community if only they didn’t rely on the incredibly slow embedded Spin interpreter from the outset and made a Spin compiler to begin with (I normally use a mix of Spin and PASM – the Propeller is Much faster when programmed assembler, albeit it’s still typically minimum 4-clocks per instruction).

These days you can get completely free and pretty fast C, Forth, etc. compilers for the Propeller. All of which are primarily Community developed – something Parallax should have done from the start. Finally, we’ve never seen the promised Propeller-II come to reality. That’s the real let down for me.

Then there’s XMOS. Don’t get me started on XMOS. I wanted to adopt XMOS – but no. Grrr…

The P8X32A isn’t cheap and isn’t the solution for high volume production, but for low volume and one-off projects it’s hard to beat. The ability to emulate a huge array of I/O hardware in software gives it a flexibility nothing else can touch.

Need eight serial ports? Propeller.

Three VGA outputs and an IIC? Propeller.

Several IIC because your date chip and EEPROMs have the same address? Propeller.

Several SPI running in separately to different RAM and SD cards? Propeller.

Three resistors and an RCA connector to get a diagnostic video display in your prototype? Propeller.

You can get cheaper, faster chips with more memory and on-board flash but nothing anywhere with this kind of flexibility. (OK XMOS maybe, but you were complaining about the cost of Propellers?) Nowadays with the Quickstart you can build I/O onto a daughterboard and easily have a workable prototype for almost any I/O configuration as fast as the PC fab can turn the boards around. It won’t crack the sub-dollar price point for 6-digit quantities, but for industry or art or a one-off hobby project it’s exactly the thing. And as Drone suggests, even if it’s not economical in production it can clarify a lot of things in development before you get to the nitty gritty of working out how the interrupt system will work in that single-core MCU.

About $30 isn’t too bad for what one gets.

Just to pick one: the STM32F413 has 10xUART, 5xSPI, 4xI2C, SDIO, 3xCAN, USB, and LCD output. So, pretty much all the propeller can do (also at the same time), plus a bunch more.

http://www.st.com/content/st_com/en/products/microcontrollers/stm32-32-bit-arm-cortex-mcus/stm32f4-series/stm32f413-423/stm32f413vg.html

Only not 3 VGA outputs, but who needs that, really ?

Quote: “not 3 VGA outputs, but who needs that, really ?”

DUH!!!, people with three eyes obviously.

“The Propeller could have been the “Arduino” of sorts for the “Maker” community ”

It can blink 8 LEDS in PARALLEL ???!!!!1111oneone.

I think they mean it’s odd in the sense that it “may not be “like” your “usual” sequential-state device you see on a daily basis”.

All these projects talk about creating single CPU logic. I think they’d call a traditional n core CPU odd too for this type of project.

Odd doesn’t mean bad. It just means “one of these things is not like the other”.

Yah, odd means different things….

What’s the odd one out… Volvo 850, Ford Taurus, Ferrari 456 and Dodge Neon.

Correct, the Dodge Neon is the only one not available as a Station Wagon (Estate, Combi, whatever)

Correct, the Volvo 850 has an odd number of cylinders.

Correct, the Ferrari 456 is the only Grand Tourer.

Correct, the Ford Taurus was the only one available with more than one cylinder arrangement. i4, V6

Whoops, forgot the V8 in the 3rd gen Taurus SHO.

Though also including the later Taurus, that makes the Ferrari 456 the only one not available with a turbo, …. though the quibble is that the Neon never was either because it was officially called the SRT4

Quote: “Maybe it seems “odd” to an relatively inexperienced Engineer”

Um, probably not considering that I started in the 1970’s.

But I probably asked for that by using a generic term such as “odd”.

It’s definitely very niche. And if you were to start building one out of TTL then things might start to get a little odd.

“The Propeller is NOT “odd”. It is really useful when applied properly…”

Things can be both odd and useful.

Maybe a noob question but If I would like to build this CPU without having to actually buy the parts (e.g., just emulating the CPU by entering the schematics into something like spice), what would be a good way of doing so (if any)? Would it be fast enough to emulate and easy enough to compile and run my own binaries on it?

I love projects like this but I don’t have space to build an electronic lab. I would like to be able to build something like this virtually.

Not sure how fast it is, but here’s a simulator: http://www.cburch.com/logisim/

How does this “transport triggered” differ from asynchronous execution? The ARM people got deeply in asynchronous experimental ARM CPUs for a while.

This is very interesting. I have a different concept for a Single Instruction Set Computer with TTA. My target is an FPGA.

The design presented here takes many cycles to perform simple operations. That would make it slow. My design uses the vast amount of hardware available in an FPGA to perform operations in a single processor cycle. I also have support for interrupts and DMA. My preliminary specifications are on Github at https://github.com/BillBohan/NISC and I really would like some feedback, suggestions, and requests for additional functionality.

FPGA is cheating lol.

Pipelining on a breadboard isn’t going to improve performance because the limiting factors are the delays on the data antenna and address antenna. So you won’t get much past 3 to 5 MHz or even less with longer wires (antennas) whereas FPGA will get you to hundreds of MHz.

The other factor is the shear number of gates. If you took what you can do in FPGA and pot it onto breadboards then it would end up a size comparable to a football field.

You project sounds great anyway and I hope you do it but it still wont compare to doing it on a breadboard.

This one goes to 25 MHz on a breadboard:

http://hackaday.com/2015/08/11/vulcan-74-a-masterpiece-of-retro-engineering/

The guy who implemented a processor with individual transistors would say that using TTL was cheating.

I had considered implementing my processor in TTL but decided to use an FPGA because TTL parts are hard to find. Where can you even get a 7489? Do they have 74S89’s?

In the 70’s I worked on Datapoint 2200 and 5500 processor boards. They were about 12″ x 18″ and had 120 to 130 TTL chips. The 5500 was the forerunner of the Z80 and it ran at 20MHz.

My project is more about the architecture than about the implementation.

http://www.ebay.com.au/itm/IC-Microchip-K155RU2-7489PC-USSR-Lot-of-20-pcs-/141922824391?hash=item210b4270c7:g:2bQAAOSwu1VW3kYh

Transistors!!! That’s cheating. We need to do it with wood and marbles!

I also worked on a process control system that implemented logic with 50 relays. The system was designed in the 50s.

That technology was still around a lot lot later.

I worked on a relay based system in the 80’s that was literally 3 stories of a building.

TTL? I don’t think it means what you think it means. Would you call an UART “RS-232”?

You all keep repeating that this is a TTL computer, but the fact is that the computer is built in HCMOS! The term you are looking for is bit-slice, 74 series MSI logic IC computer.

If you take TTL to mean the voltage levels then yes it’s TTL.

If you take TTL to mean the Transistor Transistor Logic then yes it is as the chips are Low-Power Schottky input TTL (from the schematic).

And yes they are MSI with some SSI.

There are grey areas now like HCT which is High speed CMOS with TTL voltages.

Some people even say Complementary Metal Oxide Silicon which is not correct because you can get gallium arsenide (GaAs) CMOS and MOSFET chips. It’s Complementary Metal Oxide Substrate which refers to the physical properties of the manufacturing process.

Calling this a TTL computer get the message across. Is it correct? Well that depends on who you talk to.

Sidenote: I used passive diode-resistor gates too! (see: zero detector, PC increment control logic, ACC input path selection, etc…)