The DSLogic open source logic analyzer is on its second release (the plus version) and [OpenTechLab] has a comprehensive review of the new model, which, unlike the original model, includes a different method of connecting probes and provides a separate ground for each input pin.

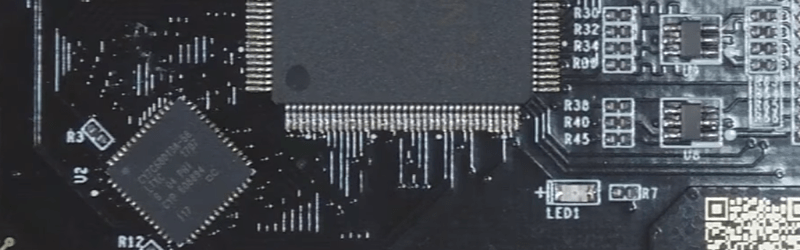

The device is pretty simple inside with an FPGA, a RAM, and a USB microcontroller. There’s also a configuration EEPROM and a switching power supply. The device stores up to 256 megabits internally and can sample 400 million samples per second on 4 of its 16 channels. [OpenTechLab] even puts the board under a microscope and maps out the input circuit.

Unlike a lot of USB logic analyzers, the new arrangement of probes and dedicated ground allows the probes to use a very short flying lead that connects to a thin piece of coax. This improves the logic analyzer, but [OpenTechLab] notes that without termination resistors, the probes can modify the signal and he even shows a simulation of the effect along with an actual comparison of normal flying lead probes and the ones provided by the DSLogic.

[OpenTechLab] was an active contributor to Sigrok, and he discusses how the original DSLogic software was an unauthorized fork of Pulseview with all the Sigrok licensing and branding removed. Some of the video covers the controversial status of the DSView software which started life as PulseView.

We reviewed the original version back in 2015. Logic analyzers are simpler than used to be, both because you rarely have access to too many internal connections and the availability of cheap FPGA hardware.

And as a part of TaD (Tutorial a Day) we’ll demonstrate some of the problems it’s good for.

That would be pretty awesome. (There was that other project something like a $10-$20 component identifier that I recollect did up to 4 pins?)

Honestly, that is damn great idea man!

I would have expected a second gen to have gone with a FX3 upgrade from a FX2 so you could sustain 400 MS/s @ 4-bits rather than just capture to RAM. It’s essentially the same hardware as the original but with better layout.

And it’s been my experience with the FX2 that an 8-bit slave FIFO path radiates less than a 16-bit path. Each have the same throughput. So I’m not sure why they put so much effort into routing 16 data lines. The 16-bit data path on the FX2 is only really for legacy 16-bit interfacing like IDE.

Right. Capturing to RAM makes the high speed mode nearly useless. But there are NO cheap options that can do it :( The Beagle Logic does that also… And everything rated 100MHz+ is usually very optimistic (awful signal integrity issues).

I’d love to see a high-end open product but I’m not holding my breath. It would need something like a fast FPGA (expensive-ish, complicated) and a FX3 (also quite expensive and only in large BGA format), along with a good front end design, quality probes, and of course a large-ish advanced-ish 4L PCB (controlled impedance, very low capacitance, low cross-talk and all). All of that adds up. Iterating that design would cost good money. Developing that would take a good amount of expertise in different fields and lots of time.

There’s companies who made it all happen (paying a bunch of good engineers and programmers sure helps!) but the end product is anything but cheap nor open.

Tested a few years ago the old model (probably 2015). At 400 MHz was unusable, because it has terrible glitches. There was no time to investigate if it was a bad hardware design, a FPGA metastablility, or just a transmission line ringing in the probes wires.

Never used it because of that.

:o(

In the meantime, ‘sigrok’ support became available. Maybe it time to test it again?

:o)

After watching the video linked in this article, even more bad news – DSLogic was using ‘sigrok’ all the time, but initially DSLogic infringed the GPL license, and they were doing it on purpose. After ‘sigrok’ team wrote them that they are infringing the GPL licesnse, DSLogic published their sources according to GPL, but in my opinion this is too late.

I don’t like these:

– false advertising (can not be used at 400 MHz sampling rate, but worked reasonably well at 200 MHz)

– initially stolen GPL software, but now they seem OK (sigrok)

– no contribution back to the ‘sigrok’ project

:o(

Also, while their client code is open on github, the firmware isn’t and the sigrok team suspects that they still violate the GPL here because they used sigrok’s FX2 firmware initially as well.

On top of that, the github commits are anything but constructive because they push one commit every 6 months, containing dozens of individual commits. It’s their strategy to comply with the GPL while making it virtually impossible to benefit from it.

Are there any active probes?

Can be easy to build using 1 poort logic ics. Would that solve the loading of the circuit under test?

anyone with a link to a working instruction as to get de original working on ubuntu 16.04? alle the links i find are or partial attempts, not complete or vor a very old version. Very fustrating

I purchased the original and the PC software was…pretty terrible. Have they made improvements? Is it backwards compatible?

While the software wasn’t amazing, it was much easier to use than the software that came with the $400 logic analyzer that my school provided me. It’s very cheap and definitely worth the price at only $50. Also, I think mine was an interim design between the first version and this version. Mine uses a 30-pin iPod connector to connect the large bank of probes to the box. I’m assuming they did this to reduce the connector on the board, it works well though.

DreamSourceLab is zero transparency company. Where and who are the developer. No information, no pictures, no location, nothing. Contact information on website only a email address. Zero activity on website and forum.

Result: zero trust. Better save money and buy Saleae Logic.

It is what it is – a quite useable cheap LA with better performance than many others at its price point. Support is no worse than any random cheap board on eBay etc, and few people complain about that. The removal of Sigrok copyrights was a dick move for sure, but open source gets forked all the time and there’s nothing wrong with that aspect. As a fork, is there really any requirement to submit code back to the original project? I’m not knowledgeable about the legal aspects of open source, but I suspect most forked projects don’t do that either (ie do Linux forks submit back to their parent Debian?).

I’ve got a DSlogic Plus, and for the money it’s proved very useful. I’ve tried Sigrok, but their DSview seems better and Sigrok doesn’t support some of the hardware options. I’ve not used any alternatives, but while researching my purchase I couldn’t find anything better for the price. And as a hobbyist, I have little incentive to spend more for the same functionality.

TLDR – There’s nothing legally wrong about it – but it’s bad for the community.

You’re entitled to your opinion, but your perspective is a disappointing one. Attitudes like yours lead to fracturing and duplication of effort in open source communities and prevent them from achieving all they could. The reason Sigrok doesn’t support DSLogic is because – as even you pointed out – DS doesn’t merge the code back in. They’re not legally required to do it – but ask yourself – how much better would both DSView and Sigrok be if the features were integrated? And who would benefit? Oh right – you.

DSL makes a decent hardware product, but similar to saleae – it’s an FPGA in a pretty aluminum chassis. There’s nothing rocket science about what DSL is producing. Buy whatever you want – but at least recognize your behaviour is self-defeating.