If you want to use FPGAs, you’ll almost always use an HDL like Verilog or VHDL. These are layers of abstraction just like using, say, a C compiler is to machine language or assembly code. There are other challengers to the throne such as SpinalHDL which have small but enthusiastic followings. [Tom] has a post about how the VexRISC-V CPU leverages SpinalHDL to make an extremely flexible system that is as efficient as plain Verilog. He says the example really shows off why you should be using SpinaHDL.

Like a conventional programming language, it is easy to find niche languages that will attract a little attention and either take off (say, C++, Java, or Rust) or just sort of fade away. The problem is you can’t ever tell which ones are going to become major and which are just flashes in the pan. Is SpinalHDL the next big thing? We don’t know.

[Tom] is pretty qualified to write this, too. He had a RISC-V design, MR1, and in comparisons, the SpinalHDL implementation was better. He wanted to know why. The post is a result of his exploration.

SpinalHDL uses Scala — an object-oriented programming language and is really a set of libraries that generates HDL. That means you wind up with Verilog or VHDL that you handle with your normal tools or you can even mix it in with conventional modules. The language proponents claim that using it generates efficient HDL that won’t cause your design to be slower or larger.

Is it worth switching? We don’t know. Is it worth a look? Probably. We actually looked at VexRISC-V recently, but not in this much detail. If you don’t like Scala, but like the approach, MyHDL is sort of like SpinalHDL but based on Python.

This triggers a memory from 20 odd years ago.

Then I read an article about a logic analyser which had quite fancy triggering.

It did that by directly on the fly programming of the triggering logic in a cpld/ small fpga, forgot what they had back then.

They also claimed that stuff like this would be increasingly hard to do in the future because of the prevalance of those higher languages and ever more hiding of the details of the unerlying architecture and programming algorithms.

I hope they were not completely right. For myself, I try to toy a bit with microcontrollers and have decided that also taking on programmable logic is (unfortunately) simply too much for my poor brain.

Cat in L’s chance

an HDL?

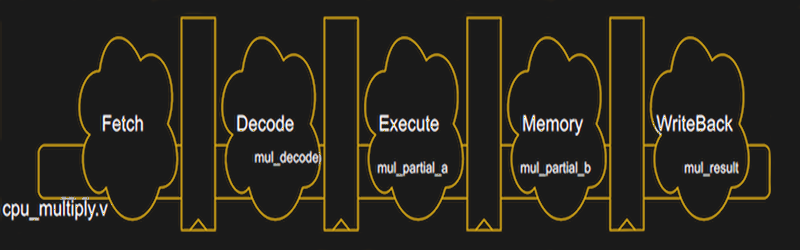

I created a processor in an FPGA a decade or 2 ago and found it quite a learning experiences. I came up with unusual problems and unusual solutions. To maximize speed in a relatively small FPGA I ended up created multiple paths for most instructions, paths that run in parallel, allowing logic to be performed during the pipeline stages. Finally the results could be multiplexed in, The problem was that multiplexing in was expensive in terms of gates and time. To speed things up I ended up with a massive and gate at the end of each bit line, Each instruction path would enter a state somewhere during the decoding, before execution to ensure that after execution all the outputs are set to 1. This can be done during the slower parts of the pipeline at no cost, due to the structure of the FPGA cells.

Knowing the underlying cell structure makes optimizations like this possible, does this software do that? I don’t know. The thing I remember most is the extremely low cost of fan out, and the very high cost of fan in, unless a simple logic function like AND or OR is used.

See my answer below.

The VexRiscv doesn’t use a mux but uses an enable (and thus an AND gate) at different places in the pipeline.

In my MR1 writers, I compare the MR1 against the picorv32 and the VexRiscv. The VexRiscv comes out as the smallest, the highest performing and the fastest clock speed.

https://tomverbeure.github.io/risc-v/2018/11/19/A-Bug-Free-RISC-V-Core-without-Simulation.html

Just curious how Spinal compares to Firrtl / Chisel which is also Scala based afaik, though Scala in the more functional rather than the object-orientated sense. And there’s also HardCaml which appears to be an OCaml HDL library. All look to be quite active.

During my Master thesis I used the language Clash to rewrite a multi core audio processing processor to generate VHDL for such a processor. http://hackage.haskell.org/package/clash. This is a compiler from a functional programming language (Haskell) to VHDL. Maybe worth looking into.