By now we should all be used to the astonishing variety of CPUs that have come our way created from discrete logic chips. We’ve seen everything from the familiar Von Neumann architectures to RISC and ever transport-triggered architecture done in 74 TTL derivatives, and fresh designs remain a popular project for many people with an interest in the inner workings of a computer.

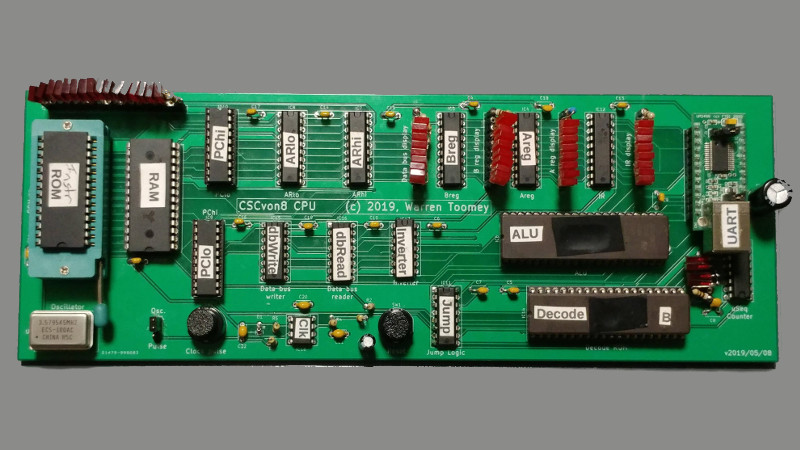

[Warren Toomey]’s CSCvon8 is an interesting machine that implements an 8-bit computer with a 64-bit address space using only 17 chips, and without resorting to any tricks involving microcontrollers. It implements a fairly conventional Von Neumann architecture using TTL with a couple of tricks that use modern chips but could have been done in the same way in decades past. Instruction microcode is stored in an EEPROM, and the ALU is implemented in a very large EPROM that would probably once have been eye-wateringly expensive. This in particular removes many discrete TTL chips from the total count, in the absence of the classic 74181 single-chip part. To make it useful there is 32k each of RAM and EEPROM, and also a UART for serial access. The whole is brought together on a neat PCB, and there is a pile of demo code to get started with. Everything can be found in the project’s GitHub repository.

At the start of this article we mentioned a couple of unconventional TTL CPUs. The transport triggered one we featured in 2017, and the RISC one is the Gigatron which has appeared here more than once.

c/64-bit/64K/

Yeah, that makes a pretty big difference.

Yep! It’s like s/18014398509481984k/64k/ (I did the math out of curiosity- 2^64/1024. wow.)

Yes. That’s 2^64 / 2^10 = 2^54, which is roughly 10^15 * 16

that uart module looks funny in the otherwise great looking built

It is a FT245 module. I’ve used them I’m my projects, and love them (except cost). It is a DIP part that keeps me from having to solder a TSOP. It also has a USB connector built in.

Implementing a large chunk of the glue logic in the form of a single ROM chip is a fairly efficient method of reducing chip count. (One can think of it as a gigantic lookup table stating what the outputs should be for a given input.)

Technically speaking, one can build a full computer with only ROM’s. Would likely not be the most speedy thing in the world, but the chip count would be very low.

https://hackaday.com/2017/02/02/the-gray-1-a-computer-composed-entirely-of-rom-and-ram/

“Instruction microcode is stored in an EEPROM, and the ALU is implemented in a very large EPROM that would probably once have been eye-wateringly expensive. ”

I imagine some remember such a trick.

http://6502.org/users/dieter/index.htm

Ben Eater’s YouTube series on an 8-bit CPU covers this and many more tricks. I recommend it highly to anybody wanting to know how computers work, at the lowest level. https://www.youtube.com/watch?v=HyznrdDSSGM&t=13s is a good place to start.

Here’re a supernice CPU that only has ROM chips for ALL of its logic and state: http://2x-1.net/ob/gray1/

I think the oddity of large-ROM based CPU implementations isn’t just their cost. It’s more that fast and large “≤70 ns” ROM chips didn’t even exist back in the day (late 1970s). Unlike SRAMs.

Well, technically there is no need for the chip to be large. An 8 bit addressable ROM can handle 8 logic inputs and usually 8 logic outputs. Then combine a slew of these chips together to form more advanced functions.

Not the most elegant way to go at things, but an array of 256 by 8 ROM cells can be constantly having their output read into a faster logic element, making for far faster reads, though at the downside of a more complicated circuit. If such “fast” small ROM chips existed back in the day is another question…

That doesn’t work out well when the stated objective is to minimise chip count of the CPU. Minimising to 1 chip is always possible with out of era chip technology. That why speed and size are important.

How fast would it be if you could replace all those ROM chips with some form of battery-backed RAM?

The problem then is programming them. They’re not all on a bus like they would be in an ordinary SRAM application. If you socketed all of them, and kept them alive with a battery when moving from the programmer to the board, which was kept powered, you might keep the programming.

/* typo */ Minimising -> Minimizing

That depends on which country you are in, Jenny List is in the UK (where actually both spellings are correct but the ‘s’ form is more common these days.)

Most Brits use the “s” spelling. My former employer, Oxford Dictionaries, has an annoying house style that insists on the “z” spelling. Go figure.

I don’t know when or why it changed, but I have a 1940s OED and that lists only the “z” endings, so it’s relatively recently. Must be something to do with joining Europe and going metric! :-P