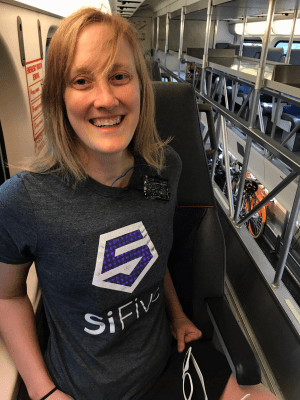

The 2019 Hackaday Superconference kicked off with a marvelous, and marvelously geeky, keynote talk on the subject of RISC-V by Dr. Megan Wachs. She is VP of Engineering at SiFive, a company that makes RISC-V processors in silicon, but the talk is a much more general introduction to the RISC-V open instruction-set architecture (ISA) and why you’d care. The short answer to the latter is the same reason you care about any other open standard: it promotes interoperability, reusable toolchains, and will result in us all having access to better and faster CPUs.

The video is embedded below, and it’s absolutely worth a watch. Unfortunately, The video is missing the first few minutes, you can follow along through her slides (PDF) and read through our brief recap below of what fell down the video hole.

Dr. Wachs starts off the talk by defining an ISA: it’s essentially the dictionary that describes all of the words that a computer speaks. When you write, for instance, a + b = c in your favorite programming language, a compiler turns this into assembly code (add a5, a5, a4), which then gets turned into the binary bits of the CPU’s machine code. The ISA covers the assembly and machine languages, defining all of the possible operations, what arguments they take, and in which registers or farther memory locations they store their results.

A common ISA is a big deal. An x86 and an ARM CPU add numbers together in entirely different ways, and this means that you need different compilers, assemblers, and debuggers to process your code depending on which chip you’re targeting. But it spreads out from there. Hardware emulators, visualizers, documentation, and everything else in the low-level ecosystem needs to be customized to the CPU’s architecture. If you think of all of the proprietary ISAs that have gone before, competed with each other, and are now gone (VAX, Itanium, SPARC, and many more), a lot of this effort is lost. And looking into the future, as more and more components get integrated into systems-on-chip (SoCs), needing to wrangle a dozen ISAs just to program a system is not out of the question. Dr. Wachs mentioned the NVIDIA Tegra SoC, with multiple DSP units for sound and audio, a video encoder, two CPUs, a graphics processor, display drivers, a USB peripheral, etc. on board, each with unique software stacks.

A common ISA is a big deal. An x86 and an ARM CPU add numbers together in entirely different ways, and this means that you need different compilers, assemblers, and debuggers to process your code depending on which chip you’re targeting. But it spreads out from there. Hardware emulators, visualizers, documentation, and everything else in the low-level ecosystem needs to be customized to the CPU’s architecture. If you think of all of the proprietary ISAs that have gone before, competed with each other, and are now gone (VAX, Itanium, SPARC, and many more), a lot of this effort is lost. And looking into the future, as more and more components get integrated into systems-on-chip (SoCs), needing to wrangle a dozen ISAs just to program a system is not out of the question. Dr. Wachs mentioned the NVIDIA Tegra SoC, with multiple DSP units for sound and audio, a video encoder, two CPUs, a graphics processor, display drivers, a USB peripheral, etc. on board, each with unique software stacks.

RISC-V (“risk five”), originally a student project at Berkeley, solves this with essentially the simplest possible, open, ISA design. A stripped-down RISC-V CPU is something that can be taught to undergrads, yet it’s also modular enough that you can include hardware multipliers and other optimizations if you feel like it. As long as you stick to the ISA standard, you’ll have the compliers, debuggers, and the rest of the software ecosystem ready for your design.

RISC-V (“risk five”), originally a student project at Berkeley, solves this with essentially the simplest possible, open, ISA design. A stripped-down RISC-V CPU is something that can be taught to undergrads, yet it’s also modular enough that you can include hardware multipliers and other optimizations if you feel like it. As long as you stick to the ISA standard, you’ll have the compliers, debuggers, and the rest of the software ecosystem ready for your design.

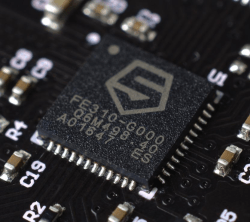

And with a number of RISC-V FPGA cores available, this isn’t just an academic proposition. You, yes you, could be playing around with actual CPU designs in a weekend, and for not very much financial outlay. Driving this point home, the badge that everyone in Dr. Wachs’ audience had hanging around their necks had not just one but two RISC-V CPUs running inside it. We’ve seen smaller and less expensive FPGA development boards that’ll fit the bill too. Sure, there’s a learning curve, but it has never been easier to climb it.

Open hardware designs are important for security, low-power applications, cutting costs, research, and generally hacking around. The last third of Dr. Wachs’ talk is dedicated to ways that you might want to use, tweak, and build on the RISC-V environment. Open standards make things smoother for large companies too, of course, and that means that you’re going to see more and more microcontrollers and even desktop CPUs running on RISC-V: open-standard hardware to go with your open-source software. But if you want to dive deeper, the most benefit from RISC-V is actually going to accrue to the hackers. Where playing around with CPU designs used to be impossible for the little guy or gal, it’s now within reach. Watch the Supercon Keynote and see if you don’t get inspired.

Megan Wachs Interview at Supercon

After her keynote, Dr. Wachs spent some time in the badge hacking area discussing the work she’s been doing at SiFive in getting from an ISA to producing chips:

So, Megan “walks” us through the RISC-V!

B^)

I look forward to watching the video.

Nice! An enjoyable overview of the RISC-V “world”. I was glad to see this finally posted since am a fan of both RISC-V and FPGAs, yet managed to miss this talk when I was at Supercon.

Thanks Dr. Wachs and Supercon peeps!

Is there any confusion about “ISA” here? Maybe I’m a fossil, but there was for me. It used to mean Industry Standard Architecture, i.e., Intel x86 period. I had to go back to the Wikipedia disambiguation page, where I find that it can also refer to the relatively super-generic term, (anybody’s) Instruction Set Architecture, which has only one word in common with the other acronym, Architecture, At which I said to myself, “Oh, she must mean the instruction set! Duh!” Well, yeah, the architecture isn’t chopped liver either.

Yep I had the exact same issue. Funnily enough I had had the same problem at work this morning with another acronym SOA I discovered pretty quick SOA to a senior manager is rather different to SOA for a tech….

Acronyms need to the outlawed!

A.C.R.O.N.Y.M

Abbreviated

Coded

Rendition

Of

Nomenclature

Yielding

Meaning

Acronyms are OK to agree. But the TLA’s need to go.

Safe Operating Area (for transistors)

Not sure if it was in the first missing minutes of the video, but she was actually super-duper clear about that in person. I tried to write a paragraph about the ISA concept to catch folks up to speed, as well.

But man, you don’t know acronyms until you’ve worked for the government…

It never used to mean “industry standard architecture”. Never. Not a single day in history. It always meant the same as it did back in the PDP-11 times.

I have to assume you are joking, https://en.wikipedia.org/wiki/Industry_Standard_Architecture

However, ISA never referred to the x86 instruction set.

My point is, the term “instruction set architecture” is much older than some niche bus spec from a then tiny PC world.

@combinatorylogic

“some niche bus spec from a then tiny PC world”

In numbers of systems the tiny PC world was larger than Any mini, mainframe, or even other micros at the time with the possible exception of the Commodore 64. AKA it was far from niche.

Yes ISA did stand for instruction set architecture first but it also meant industry standard architecture. You can probably still get ISA bus connectors today on some x86 motherboards. In fact here you are.

https://www.nixsys.com/shop/parts-accessories/legacy-motherboards/?gclid=EAIaIQobChMI6PbI6vWm5wIVBpSzCh2yzQFUEAAYASAAEgKW4fD_BwE

>Where playing around with CPU designs used to be impossible for the little guy or gal, it’s now within reach.

Not quite the case. There were a lot of people working on implementing processor in FPGA projects before RiscV. The biggest problem with these projects are software side: i.e. compilers and ability to port software afterwards. So up till now most of these projects are the older more well supported CPU cores (e.g. 68000 or variant for Amiga/Atari ST) and smaller 8-bit (AVR, PIC, 8051 etc).

The push to RiscV and main stream toolchains means that these people can work on the hardware side of larger and more modern architectures knowing that they can easily port software to their system.

The openness of RiscV also has its down side as each implementations can have their own custom instructions for optimizing certain operations. Let’s see if they can come up with some sane library standards that abstract aways some of these differences while taking advantage on systems that do support them.

OpenRISC toolchain was fairly mature long before RISC-V. And a lot of people implemented MIPS variants for the same reason.

And you will be lost to china as you may note even a light switch can run these … and they need an open one to easy to get to (and … not sure about share in bad. The question is not any plan not to, just competitive in hardware is …)

Good luck and thanks you for the fish.

“When you write, for instance, a + b = c in your favorite programming language”

I assume that is comment bait, which I have now fallen for. Doh!

Haha. Nope. Just me being silly.

“lvalue required as left operand of assignment”

Clearly what I meant was “a + b => c”. (Name that statistical programming language.)