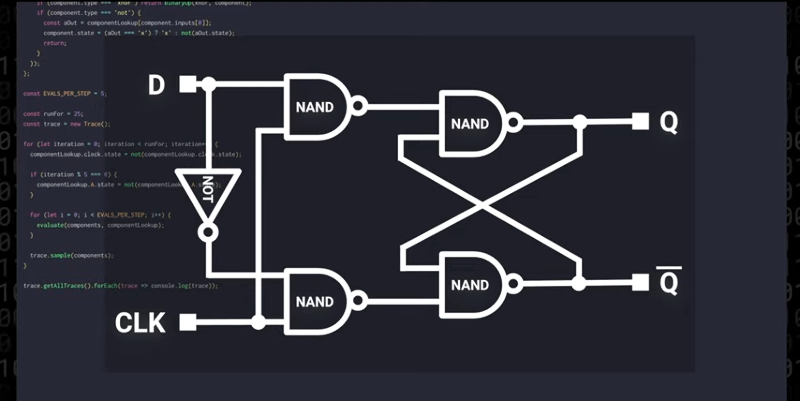

How do you celebrate your YouTube channel passing the 7400 subscriber mark? If you are [Low Level JavaScript], the answer is obvious: You create a 7400 TTL logic simulator in JavaScript. The gate simulations progress from simple gates up to flipflops and registers. You could probably build a 7400-based computer virtually with this code.

In addition to just being fun and interesting, there were a lot of links of interest in the video (see below) and its comments. For one, someone watching the channel took the code and made a Verilog-like IDE that is impressive.

Granted, you could just go to EDAPlayground, write some Verilog, and simulate it using normal tools. Somehow, though, that doesn’t seem as much fun as virtually connecting 7400 chips together. Don’t ask us why.

There’s also a link to an impressive open source web-based logic simulator. You can grab the code for it on GitHub if you wanted to make modifications or just look at how it works.

The video mentions that [Ben Eater’s] breadboard computer was inspiring for this project and we’d love to see someone do a simulation for the browser using this kind of technology. If you want to see an even more primitive computer simulated in your browser, try GENIAC.

awesome

Let’s not forget http://www.falstad.com/circuit/circuitjs.html !

Or http://www.messydesks.io

Does it emulate gates well enough to do latch-up?

The only thing to do, is build a computer in it, and an implementation of JavaScript.

.. and then run this simulator. After that, slowly and carefully pull out the actual computer out from under it, and voila!

Some still build 7400-based pll networks, i believe, since pll-specific chips come and go. Might be using new variants of different ‘mos’ technology at higher speeds, different voltages, but you get the drift. Still very useful. No ridiculous programming chains, etc…

Hurray! Now if someone can UNCLUTTER the madness.

and figure out what series and families are compatible with each other.

On the current plane AND the speed plane.. that doesn’t require a PhD in Comp Sci, Electronics AND Historical Referencing of product and manufacturers… that would be superb.

They only “look” like Lego toys… they are VASTLY complex.

https://en.m.wikipedia.org/wiki/List_of_7400-series_integrated_circuits

have a look at TI’s Logic Pocket Data Book:

https://www.ti.com/lit/pdf/scyd013

The 40L and 40 on page 53 nice chip..

But YEAH… pg 157 indeed covers the some of the 74xx family functions.

The issue I mention without getting into a detailed description is visible with that reference book .pdf

Say, you wanted to build an 8 bit ALU unit and wanted some memory storage/access. One would have to cherry pick a family path that wouldn’t be exclusive to one technology tree.

And have to mix/match balance the TTL, LS, S tech class along with some AC or ACT (or even the AHS).. to get to you end design goal.

From what I remember each of those family of chips, have a different voltage requirement, different clock speed and different speed of execution.

Save those old copies of Windows 10/Linux Xilinx ISE 14.7!

REMEMBER AMD just ponied up $40 billion for Xilinx don’t be surprised if the old tools disappear!

Voltage is pretty straight forward, and current is at least in the context of between 7400 chips.

HC in one hand, LS and HTC in the other. If you want a simple rule, just don’t mix them.

Not sure what you mean by compatible so far as speed. Isn’t that dictated by what you’re making? Or do you mean something other than lowest-common-denominator?

Clock speed.. nano seconds vs pico second levels.

There are fairly comprehensive 74LS and 74HC libraries available for LTspice. They are behavioral models but if I remember correctly you can specify rise/fall times and for the HC lib at-least, the voltage level. The libraries and usage/install instructions should be in the files area of https://groups.io/g/LTspice