If you’re anything like us you’ve been keeping a close eye on the development of RISC-V: an open standard instruction set architecture (ISA) that’s been threatening to change the computing status quo for what seems like forever. From its humble beginnings as a teaching tool in Berkeley’s Parallel Computing Lab in 2010, it’s popped up in various development boards and gadgets from time to time. It even showed up in the 2019 Hackaday Supercon badge, albeit in FPGA form. But getting your hands on an actual RISC-V computer has been another story entirely. Until now, that is.

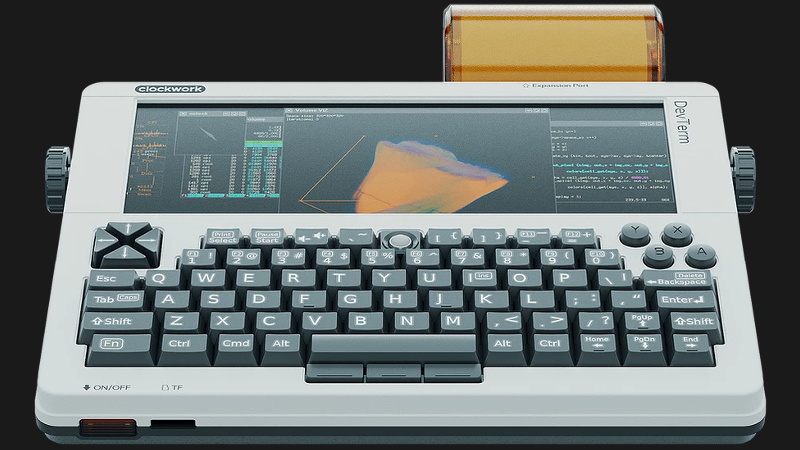

Clockwork has recently announced the availability of the DevTerm R-01, a variant of their existing portable computer that’s powered by a RISC-V module rather than the ARM chips featured in the earlier A04 and A06 models. Interestingly the newest member of the family is actually the cheapest at $239 USD, though it’s worth mentioning that not only does this new model only include 1 GB of RAM, but the product page makes it clear that the RISC-V version is intended for experienced penguin wranglers who aren’t afraid of the occasional bug.

Beyond the RISC-V CPU and slimmed down main memory, this is the same DevTerm that our very own [Donald Papp] reviewed earlier this month. Thanks to the modular nature of the portable machine, this sort of component swapping is a breeze, though frankly we’re impressed that the Clockwork team is willing to go out on such a limb this early in the product’s life. In our first look at the device we figured at best they would release an updated CPU board to accommodate the Raspberry Pi 4 Compute Module, but supporting a whole new architecture is a considerably bolder move. One wonders that other plans they may have for the retro-futuristic machine. Perhaps a low-power x86 chip isn’t out of the question?

The specs sound very much like it might be based around an Allwinner D1.

It is. The raspi-compatible(?) SoM can be had for about 30 bucks and *theoretically* the RTL for the core is on github.

https://www.talospace.com/2022/03/the-first-production-risc-v-portable.html

To be fair, it does have some modern video decode codecs. While 3D will be snails pace, it should be possible to watch videos without issue.

It is odd that they do not explicitly say that the CPU is a Allwinner D1. Imagine buying a laptop without knowing model of Intel, AMD or a Zhaoxin x86-64 CPU was inside.

Yeah. I noticed later that the D1 module was on the store, until then I was basically in guessing territory based on:

* Knowing the D1 is usually at ~1GHz

* Knowing the D1’s ISA is RV64IMAFDVCU (note the U there, which denotes user-mode, which isn’t a super common way to denote that. The D1 is regularly listed this way.) (Also the vector extension is a prefinal implementation that isn’t fully compatible with the Vector extension spec as it currently exists, but that’s a side note)

* Knowing the D1 doesn’t have a 3D GPU, fulfilling “No GPU” though it does seem to have some 2d acceleration and image decoding stuff

It seems a little bit ridiculous to not state this on the page for the Clockwork Devterm itself, or at least leave a link to the module in the store, though admittedly it doesn’t list the screen resolution either, which I would really expect as a minimum… The A04 and A06 pages don’t list that either, though it’s not super hard to find that it’s 1280×480.

I’m not sure if being a hacker product makes it better or worse that the actual CPU core isn’t immediately listed. In some ways it might be understandable given the “Don’t buy this if you’re a newbie” disclaimer that you should really be researching it before you buy it, in which case you’re going to find the module in their store and discover the D1 at the gooey caramel center. In some ways it feels like it makes it almost worse since it seems like it’s almost an obfuscation the CPU that’s present in this version of the DevTerm.

It might be nice to have a disclaimer about some of the specific hangups of this particular chip on the page, along with the “Newbies please don’t buy this” warning, for instance the nonstandard Vector extension implementation (which might force most programs to just run as RV64GC if they’re precompiled), also the fact the linux support isn’t upstreamed, and the overall GPL noncompliance issues which I normally wouldn’t see as a big problem, except for the fact that it’s now operating as the brain of a “Hacker” portable which is pitched as OSHW.

https://linux-sunxi.org/Allwinner_Nezha#General_Notes (intro paragraph)

I hear that the first run will be an FPGA implementation while they work on integrating a hard SOC.

“Persona non grata”

About the picture caption: yes, I know it’s meant as humour. That’s OK, but it might intimidate someone. We people are like that.

Perhaps “newbies are going to learn a lot”?

Otherwise… if I just currently had the disposable income, I’d order three. Yikes!

It is a fair warning that should intimidate newbies because doing otherwise would likely do them a disservice. There is no need to sugarcoat that the software is going to be a work in progress for a while.

The point is this is only for people who actively *want* to mess around with RISC-V, because it will be necessary. It’s absolutely appropriate to scare people off who are likely to just want a working device; they should be getting one of the other options.

Interesting. I note that one can buy a Zynq FPGA as a SODIMM module, and the webpage does mention the possibility of using FPGA in passing – I wonder if this is where they are going? That one can upgrade/swap the processor module is a nice touch in any case.

I suppose it would be nice to design and implement one’s own CPU and OS kernel.

i wayting for orange crab or similar fpga

and GOOD KEYBOARD!

Putting x86 in this makes no sense. It’s really time we all weaned ourselves off this awful stack-of-crap architecture. Almost any other would be better.

Agreed, although I would miss FreeDOS on newer devices, I’d be worth it.

DOSbox ensures you always have DOS.

RISC-V is dead isn’t it?

Sorry, what?

I don’t know where you heard this, but RISC-V is far, far from dead. In fact, it’s just getting started. Companies are releasing RISC-V MCUs left and right. It takes a long time for a new ISA to be standardized and adopted, and we’re just getting to the juicy part.

Now actual Linux-capable computers are going to take a bit longer, but that’s also happening. First it’ll be budget ‘multimedia’ SOCs like Allwinner, and then probably high performance cluster CPUs, and then eventually low-end laptop CPUs, and then finally a company like Apple or AMD might adopt it for high performance consumer gear. Be patient, it’s a whole process.

They are also dropping RISC-V projects right and left. Allwinner dropped D1. Devs have all bailed on StarFive, and …. Sorry, but it reeks of other dead CPU/instruction sets. Unless some new deep pockets step up it might be relegated to ASIC and FPGA implementations. Given that ESP32 is a couple dollars and the STM32 family is filling in on the upper side with Linux capable products, well, good luck.

RISC-V is more alive than ever. Multiple Linux SOCs coming out, widely implemented edge solutions, more and more MCUs, a lot of big things happening in the compute world.

I have no idea what an “edge solution” is. Is it something to handle a boundary condition? Anyway, few things would please me more than to see success but all I see are people abandoning their interest.

The picture has a cool old-school Unixy look to it with.. what is that? TWM?

If ever there was a form-factor made for made for a keystroke based tiling window manager though… I’m just imagining trying to resize and position TWM windows with that thing!

Just my 2¢ but I’d definitely suggest trying Stump if you buy one of those.

I think they had a broken Tandy Model 100, and gutted it.

B^)

The layout reminds me of the old typewriter style word processors…