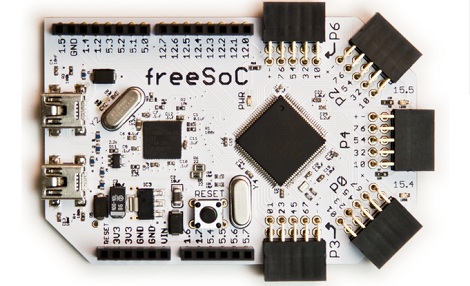

Like many of us, [Jon] began his journey through the magical world of microcontrollers with an Arduino. For a beginner, the Arduino is a wonderful tool, but [Jon] quickly found himself limited by the platform. There are too few pins on the Arduino, and and the platform doesn’t really lend itself to extremely complex projects. To this end, [Jon] designed freeSoC, an Arduino-compatible platform based on the Cypress Semiconductor PSoC 5.

The Cypress PSoC 5 is an extremely capable microcontroller with 60 general purpose I/O pins and 8 special purpose, high current outputs. Every pin on [Jon]’s freeSoC is completely configurable; if you want 24 SPI ports and a dozen 20-bit ADCs, just launch Cypress’ design software and configure the chip graphically. With this many I/O ports, the PSoC 5 is as useful as an FPGA, without all the hassle of actually being and FPGA.

A really neat feature of the freeSoC is its ability to be programmed graphically. Using Cypress’ PSoC Creator IDE, the multitude of I/O pins can be configured to just about anything very easily. Because the PSoC 5 is based on an ARM Cortex-M3, programming the freeSoC is as easy as any one of many ARM dev boards that were recently released.

[Jon] came up with a very, very neat project here, and it’s something we can definitely see the utility of.

Thanks [Dale] for sending this one in.

This is not as capable as an FPGA. FPGAs can run all the logic behind their pins concurrently. Microprocessors run their code sequentially. Which means you can spend hours trying to get the behavior you want when the code is executing in the wrong place to trigger the behavior you want.

I’ll admit that FPGAs are a hassle for first time users and that an Arduino style kit would work wonders for their hobbiest adoption, but they are well worth the learning curve. Try out the MachXO dev kit.

Oops. Just read the datasheet. it does have pld logic behind it. This looks like a nice device.

It’s very expensive for what is effectively a run of the mill ARM with a tiny CPLD attached. A cheaper FPGA plus a mediocre SPI DAC/ADC and some free IP off OpenCores.org will give you a much more powerful platform. And the FPGA design only needs to be done once if all you want to do is code software for it.

There are not just PLDs. Each UDB (digital block) contains also an ALU and 4 byte FIFO. They can be used for creating new types of peripherals, or extend the existing ones (e.g. with 24 UDBs you can create 12 16bit-PWMs, if you need them).

Whats also has been missed is that the PSoC contains many analog elements, like OPAmps, analog Muxes, 3 ADCs, severals DACs, filters and so on. Actually I once build a complete analog-digital scope (2 channels analog, 8 channels logic analyzer, up to 1 MSps, configurable triggers) on a single chip, without external components.

Has anyone tried PSoC Creator, what do they think of it? Does it run under Linux? Are arduino libraries compatible? Etc..

“Is the PSoC Creator IDE Mac and Linux compatible?

PSoC Creator is a Windows-based IDE.

However, I exclusively use Macs, and I use Virtualbox for my development with PSoC Creator. I’ve used both Windows XP and Windows 7 successfully, and I actually prefer doing this to a pure-Windows approach.

The reason for this is that when developing a USB project, I can program and debug in Virtualbox, and then use libusb and PyUSB (both mac/linux compatible) to communicate with the freeSoC without having to go through the hassle of installing a driver for the device.

The system requirements are pretty minimal (1GB RAM, Pentium 4 processor or better), so any modern computer will run it no sweat.”

amazing combo of software+hardware…

Nope!!

The Cypress software only runs under windows.

But that is why god created VMware.

It is also possible to load the Cypress boards from java, with the addition of a small Library.

Where these devices pay off, is the ‘offload’ capability, where you can configure I/O to directly load/dump the USB buffer data without needing the CPU to handle the loading of each data byte.

Then there is the ‘re-numeration”, where the device has multiple USB ID’s., when connected it has one ID which allows the device to be loaded, it then disconnects and re-numerates with another ID signaling that it has been programmed and is ready to use.

OR, you can pre-load firmware into an external EEprom to be used on startup.

Add into that the capability of some of the other modules and you have a powerful device.

This is cool. He hasn’t posted the PDF schematics yet. Does anyone know what the programming chip is? Is it special-function only or programmable as well?

It’s a Cypress EZUSB FX2LP, PN: CY7C68013A

No PDF, but the eagle-format schematics+pcb are at https://github.com/freesoc/freesoc/

It says it’s a Cypress CY7C68015A on the schematic, which is part of Cypress’s FX2LP family, the same as the CY7C68013A but with a couple of extra IO pins. But only 4 IO pins seem to be used total, and it doesn’t look like any of the unused pins are broken out on the board, also it’s QFN so breaking out the unused IO manually would be challenging. Still, it does have an 8051 core (SDCC can be used) and a USB2.0 HS interface, and can be reprogrammed via USB.

In fact the schematic only shows a 24LC00 for the EEPROM, so it’s likely being used to store only the USB VID/PID information and the firmware will be loaded into the chip’s memory by drivers on your computer via USB every time you plug it in (like a Saleae Logic Analyzer does, which uses a CY7C68013A + 24LC00). It’s possible that it’s using the same chip and same VID and PID as an official Cypress PSOC programmer so that Cypress’s official drivers and firmware can be used directly. I don’t mean to equate this with the defacto piracy of a Saleae clone, but if you’re familiar with the hackaday posts about those, it’s basically the same mechanism that those clones use by including a CY7C68013A and an EEPROM with the official Saleae VID and PID to trick the official Saleae drivers into loading the firmware onto the knockoff.

Which is to say it is a general purpose chip, much weaker and less interesting than the PSoC5, but with a very fast USB interface. But it doesn’t look like reprogramming it would be too useful with its limited connections, unless you aren’t looking to do any I/O and are just looking to use the processing power of an 8051 on the end of a 480Mbps USB interface :)

If you do want to play around with an FX2LP chip, a better option is probably one of the tons of identical CY7C68013A breakout/dev boards on ebay for under $15 shipped, which is probably cheaper than you can buy the chip alone in small quantities anyway. The ’13A has two fewer GPIOs than the ’15 on the FreeSOC, but on the other hand all of the GPIOs on the dev boards would be broken out :)

But the PSoC5 is definitely the main attraction here.

Thanks Nick. That makes sense. He mentions help from a grant from Cypress for his first prototype of the PSoc Mini. Maybe this programmer is compatible with the official Cypress programmer as you suggest (MiniProg3?). No link to firmware for this device so I wonder if it’s considered confidential Cypress IP. Sadly that makes his open hardware design a little less open since one couldn’t (re)design their own version. Unless I’m mistaken about availability of the firmware.

In case it wasn’t clear, the freeSoC project is on kickstarter:

http://www.kickstarter.com/projects/18182218/freesoc-and-freesoc-mini

I am a backer on kickstarter but have no other affiliation.

I would like non-windows software for the Cypress PSOC chips, but Cypress has not ported their software to other O/Ses.

Hey Guys, Glad my submission got posted. I came across this recently and I pledged a handsome amount to get it off the ground. Thanks H@D.

Pricey for something that lacks things as reverse current protection or current limiting. Overall, not too bad. Would prefer screw terminals though.

On a somewhat unrelated note:

High-current opamp: 10mA

High-current GPIO: 20 or 30mA, depending on where in the datasheet you look

High-current DAC: 2mA

Which of these values justifies the stressed “High current” moniker?

I know that high-current CMOS and high-current bipolar are different worlds, but still – most of my hardware (pic, arm, fpga) are between 16 and 25 mA peak current. Am I missing anything here?

“Every pin on [Jon]‘s freeSoC is completely configurable; if you want 24 SPI ports and a dozen 20-bit ADCs, just launch Cypress’ design software and configure the chip graphically. With this many I/O ports, the PSoC 5 is as useful as an FPGA, without all the hassle of actually being and (sic) FPGA.”

No. No. No.

There is ONE 20 bit ADC. You can multiplex on the input to it but you can’t have more than one. And there’s a limit to SPI ports too – I’m not sure how many of the data blocks one of them takes but it’s probably more than one. Anyway, the idea of having 20 SPI’s is silly. One SPI and a bunch of selects is the way to go. SPI does not allow a peripheral interrupt so what good does it do to have twenty of something that the processor can only use one at a time? Obviously that’s nonsense.

This was written by with more enthusiasm than knowledge. I’m not saying the PSoC isn’t a good chip – just that I have an expectation that the people writing these entries know what they’re talking about.

And EVERY pin is not COMPLETELY configurable. Obviously the power and grounds are not. And the high current digital pins are not. And the best analog performance is achieved by using certain pins. It’s highly configurable.

Thanks for grounding us all. I’m on the road so I havent found time to read the white sheets, but I just about creamed my pants when I saw those claims.

Thanks, I cringed while reading the article summary as well. I’m sure the Cypress FAEs would love for us to think that is true, but practically, you have to check the HW design guide + errata to see what pins are best suited for your application.

Why can’t HAD fact-check for like 30 seconds :(

>This was written by with more enthusiasm

>than knowledge.

That could be applied to almost every article on hackaday..

Those radially-arrayed headers are pretty clever.

What would be even more clever is a layout with one 50-pin header that allows you to use a single ribbon cable for all your i/o.

Yeah, I’m fun at parties.

When even an Arduino is expensive and wasteful for what it is, you want $64 for “an Arduino with more IO”? This is not acceptable. And don’t respond with “Oh you get more than that!” because that’s not how it’s being advertised. Esp. considering you can get ARM chips for $1 now…

If you want to simple approach, just buy the damn AVR chips and use them raw — if you need more IO get some 74HC165 / 74HC595 (you can buy them in bulk very cheaply — I think it was like ~$8 for 25 of them on digikey last I ordered?).

If it’s anything like PSoC Designer then every release will break something in old projects. Thanks but no thanks. I went to Microchip and I’m not going back.

I’m waiting it out on this one.

It looks good, the price may be a bit high, but I haven’t done a cost analysis yet to see if it’s in the right ballpark.

It looks like it’s using the official programer firmware from Cypress, which from what I can tell is within licensing agreement.

It’s not using jtag as the interface though, at least from what I can see.

Hi, I have developed a PSOC 5 Board for teaching and Prototyping ! It is designed for CY8CKIT-059 from Cypress !

Her is a link to the Board http://www.bernhardt.de/wp-content/uploads/2020/02/DSC00875-1152×1536.jpg