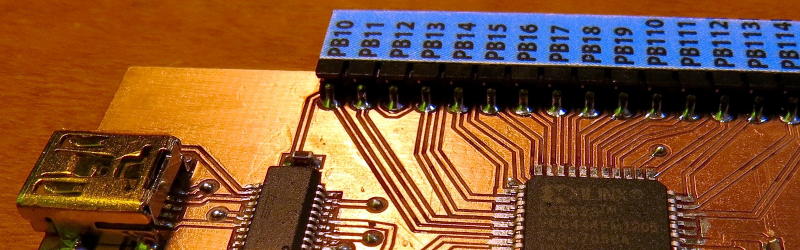

[Kodera2t] wanted to experiment with programmable logic. Instead of going with an FPGA board, he decided to build his own CPLD (complex programmable logic device) board, with a built-in programmer. The CPLD is a Xilinx 9536 which is inexpensive and, though obsolete, still readily available. The programmer for the board uses an FT232RL and the total cost is very low ([kodera2t] says it is in the price range of a Raspberry Pi Zero or about $4).

From a user’s point of view, a CPLD is just a small FPGA. Internally, there is a significant difference in how they implement your design. Although there are differences between different product families, CPLDs usually use a sea of logic gates arranged as an AND/OR chain. By feeding inputs and inverted inputs into the AND gates and then ORing the results, you can build interesting logic circuits. However, modern CPLDs use Verilog or VHDL, so you describe what you want just like with an FPGA and the software figures out how to use the underlying circuits to give you what you want.

FPGAs typically use a different method to represent logic, usually LUT or Look Up Tables that amount to truth tables, defining outputs from a set of inputs. However, other FGPA architectures exist (such as mux-based FPGAs). FPGAs usually have more flexible interconnection than a CPLD. From a practical standpoint, though, you can consider a CPLD as a “little” FPGA. CPLDs almost always hold their own configuration in non-volatile storage, so they come on instantly; only a few FPGAs do that.

The [kodera2] project on Hackaday.io has pretty thorough instructions for programming and also has a PCB layout for the board. The $4 price point is hard to beat, but a much more capable FPGA board doesn’t have to cost much more than that. However, if you want the experience of building everything from the PCB up, the CPLD project lets you get something up and running with a small investment and without having to solder super dense parts. On the other hand, if you just want to learn Verilog or VHDL, you don’t need any hardware. Just use your web browser.

There’s a short video of the board in action, below.

It would be nice to have some decent programmable logic, smaller than the current FPGAs, and with integrated configuration memory. Unfortunately, CPLDs are too limited, with only a few dozen flip flops, narrow OR gates, and no carry chain logic.

Try cypress psoc?

They are in the different market – microcontroller plus glue analog/digital logic. They are primarily microcontroller *first* plus a few programmable analog/digital components and very tiny amount of programmable logic.

The size of the programmable logic is the old PAL chips. It is even more restrictive than the lowest end CPLD on the market.

I was looking at the cypress psoc for my project but not having any experience in FPGA’s was trying to find someone who could cast a little light as to if this would be an option. I am trying to run 1 X stepper motor in a kind of closed loop with a pot as a speed controller and have an LCD screen with buttons as the interface. at the moment the project is sitting on a nano but I am running on to some speed issues.

You could implement the speed controller pot part in the hardware section of the psoc and handle the lid part in software. They have a lcd component. They have a bunch of videos you can check out.

Why not just use a faster micro? This seems like a job for an ARM or Propeller or something along those lines. CPLDs and FPGAs aren’t very well suited to dealing with analog input such as that from a pot, but it can be done using a sigma-delta conversion with some extra components. Lots of ARMs out there have powerful ADCs like ATMegas do, so it’s probably easiest to go to an ARM platform and see if that meets your needs before going to anything more extreme.

there is an ARM in PSOC MCUs (cortex M0 or cortex M3, depending on how beefy you take it), and ADCs, and op amps, and capacitive touch.

FPGAs are often used for motor control. Switch out the pot for a rotary encoder and you don’t need to worry about analog.

I’m writing a tutorial on how to make a PSoC VGA Controller with Verilog.

It’s not finished yet but It can display video already.

http://www.eevblog.com/forum/projects/no-bitbanging-necessary-or-how-to-drive-a-vga-monitor-on-a-psoc-5lp-programmabl/30/

It’s a bit limited as far as a cpld but you can optimize your verilog to map better to the UDBs and Datapaths, but I’m not going to address that in that tutorial, I’m letting the toolchain figure things out for me, but it can be squeezed to make better use of the resources.

But you can always use their modules that even include a full graphical lcd. But to learn basic Verilog is an affordable kit for just $10 with full debug. Alas Windows only.

It is funny Miguel, I actually already have a post pending on your excellent PSoC work. Ought to hit the front page in a few days.

Wow, thank you, I’m honoured!

It’s still work in progress, with lots to do, like the EEPROM character set and the DMA and frame buffer.

I’m discovering PSOC, the Cypress MCUs at the moment, they are interesting at least form my beginner’s point of view. You can configure some blocks to chain the carry to make wider operations.

Check out Lattice’s XP2 line of FPGAs. They have instant-on internal flash and can do quite a bit.

CPLD’s are not too limited, do not only have a few flip flops, and you can set carry chain logic just like you can in an FPGA.

There are some very small CPLD’s, but there are also some very large CPLD’s like Lattice’s MACHXO2 and MACHXO3 series devices.

The MACHX02 looks interesting, but most of the small devices are 0.4 mm and 0.5 mm pitch BGA, which is too small for my taste. There’s one QFN, which seems okay. Thanks.

There are also a bunch of TQFP MachXO and MachXO2 parts. They’re pretty big, but easier to solder.

I saw, but I was looking for a device with less I/O but still quite capable in logic. As soon as you move to the larger packages, then I could already get an FPGA.

+1 on the MachXO2 and XO3 series from Lattice Semiconductor. Thing to remember with these devices (among other things) is they are more FPGA-like internally than CPLD ie. many more (but smaller) LUT-based logic blocks versus typical CPLD macrocells, more user-configurable flip-flops, different interconnect matrix etc.

I’ve used them for several projects now over the years and they work quite well. :-)

The XC9500XL series PCLD used in this board has one advantage that wasn’t mentioned. While it is not as shiny as some of the newer generation of CPLD that has memory, PLL etc, it is 5V tolerant 3.3V CPLD that is still in production.

I also love these CPLDs… lots of package styles, speeds, etc. Sadly, Xilinx has indicated that XC9500XL family will be discontinued in 2017… argh… Their “replacement” is the CoolRunner II (CRII) family. They are similar (packages, most of the pins are the same, etc) but… the CRII parts are not 5V tolerant, require a 1.8V supply for the core, and have less resources (Macrocells). The positive thing is that they are supposed to be in production until 2022.

I recently took a look at the overall CPLD offerings and it looks as if the main players are abandoning CPLDs in favor of larger capacity FPGAs. This is too bad, as not everyone wants a monster FPGA nor does everyone want FPGA’s vendors embedded MCU.

Actually, an FPGA combined with Cortex-M4 core… would be nice.

The main aim being – a chip that can be implemented without needing a 4 (or more) layer PCB.

the coolrunner 2 CPLD are also fased out. A salesman told me last runs were made in 2019 i think. Because CPLD’s don’t scale to the new silicon technologies as an fpga does. So it doesn’t make sense to keep manufacturing them… They are already about as expensive as an fpga that’s more performant (but sadly also more complex to embed in a project)

What we really, *really* need is a campaign to get programmable logic manufacturers to open up FPGA/CPLD/SPLD development. That means: Open programming algorithms and proper open design tools.

It’s truly astounding that the hobby or semi-commercial hack community cares about open development at all scales, but we’re pretty much oblivious to the fact that we’re dependent on proprietary tools and dev systems to get any programmable logic off the ground. This has to change: we don’t need the most advanced programmable logic at the hobby level, but the community deserves to have an open programmable logic platform.

http://www.ecstaticlyrics.com/electronics/ATF22V10C/

MMI open-sourced (before there was such a term) PALASM, and provided the information needed to program their devices. Lattice provided the GAL device programming information, as did Cypress for their UV-erasable EPROM PALCs.

This sort of information needs to go into a Wiki somewhere– pldwiki.org, anyone?

Great link! You’ll find a few more sources on my web page for these older devices. As I have a small stash of Cypress PALC22V10s, I’m looking at building a programmer for that.