Open Source software has been around for decades. Over these decades, Open Source software has been the driving force behind most of the Internet, and all of the top-500 supercomputers. The product of the Open Source software movement is perhaps more important than Gutenberg’s press. But hardware has not yet fully embraced this super-charging effect of openness. Being able to simply buy an open source CPU, free of all proprietary bits and NDAs is impossible.

Now, this is finally changing. OnChip, a startup from a group of doctoral students at the Universidad Industrial de Santander in Colombia, have been working on mRISC-V, an open 32-bit microcontroller based on the RISC-V instruction set. It’s now a crowdfunding campaign, and yes, you can simply buy an open source chip.

We’ve taken a look at onchip’s Open microcontroller project before. The team has made significant progress of moving from something that can run on an FPGA to the tapeout of a real, physical chip. The onchip twitter timeline is a flurry of activity, with real silicon and a prediction that 50% of low-end microcontrollers will be running RISC-V in a decade.

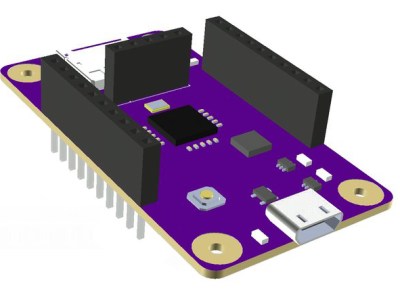

If you want to get your hands on one of these open microcontrollers, the Crowd Supply campaign is actually fairly reasonable, considering this is custom silicon. $49 USD gets you a first-run mRISC-V in a QFN-32 package. $99 gets you the mRISC-V dev board with an SD card slot, USB, regulators, and of course the micro itself.

This chip’s capabilities are almost on par with a low-power ARM Cortex M0. The chip itself runs at 160MHz, has SPI, I2C, SDIO, and JTAG, as well as a 10-bit 10MS/s ADC and a 12-bit DAC. There are 16 GPIO pins on mRISC-V. You won’t be able to build a smartphone or laptop with this chip, but you will be able to build an Internet of Things gizmo.

While OnChip’s efforts won’t result in a completely open source smartphone, there are other projects in the works that will bring an Open Source core to more powerful devices. lowRISC is a project to bring a Linux-capable System on Chip to production, and various people smarter than us have brought GCC, LLVM, and QEMU to the architecture.

Most of the efforts to bring the RISC-V architecture, and indeed most Open Source processors, have focused on the big chips — full CPUs and SoCs. Onchip’s mRISC-V goes the other direction to create a small, open microcontroller. If you’re looking to create an ecosystem of Open processors, this makes a lot of sense; there are more Honda Civics on the road than Lamborghinis, and Microchip and TI ship far more microcontrollers every year than Intel ships CPUs.

The lack of flash on-chip and the need for multiple supply voltages makes this chip anything but “simple replacement for cortex-m0 class chips” as they claim. It may get there someday, but it i snot nearly there today. Nice progress though.

I kind of like the way the ESP8266 doesn’t include flash. It lets the design dictate the size you want to include rather that requiring a full-line of what is basically the same chip with different flash sizes.

sounds nice but has a big downside: external serial flash memory can’t beat onchip flash memory in speed especially for random reads.

I think it is a matter of time before they add flash and ram in huge amounts ;)

Thanks for the comments. We are working hard to get most of the circuitry open to people. Students and curious people would be able to contrast silicon layout with transistor level schematics. Double-gate (EEPROM) is expensive by license and by fabrication. We are diving deep to solve this, by doing an extra effort on designing our own NVRAM cells (single poly) and try to virtualize RAM with the limited NVRAM possible. NVRAM is area expensive and if we reach the goal of $500k plus an additonal $200k you would see speed that you cannot see on regular micros. This is the reason of open source, work around things and do better than closed commercial chips. Long term goals can be near-term goals, it is in your hands.

Apparently on-chip flash cannot beat onchip-sram in speed, especially for random reads…. :-)

The ESP8266 has a bunch of extra RAM to load the off-chip program code into. If the on-chip RAM is not enough, you need a bigger flash chip as well, and you can arrange for part-of-the-code to be in RAM, where the “only when … ” code is left on the flash chip.

Did you know that seagate harddrives work similarly? Almost all of the code starts out on disk, but those parts used “now” are loaded into RAM.

ahh… no – sorry, mike. if you’re saying what you’re saying then it is a high probability indicator that you’ve never designed a board with an embedded microcontroller before. the board space, cost and inconvenience of not having on-board flash and not having simple power management far exceeds the “cost savings” and even the proposed “open-ness”. remember: there’s hardly a single embedded controller out there that doesn’t already have libre source code and support libraries. take a look at libopencm3 and other projects to find out quite how many ECs are supported by the software libre community.

to give you an example: i refused to use the STM32F070 because the STM32F072 has a “PLL sync” mode which stabilises the on-board (slightly inaccurate) crystal using the incoming USB port. very very smart idea that saved me having to put down an extra five components (one of them a 3225 crystal)…. but it was ESSENTIAL to that particular board design that i SAVE THAT SPACE.

now, if there are over 15 to 20 extra components required to add an external flash IC and extra power domains, how the hell is anybody who KNOWS WHAT THEY’RE DOING supposed to use this processor and be able to keep their jobs? not only will it cost far more but their boss will tell them to go get it done with a better processor.

it’s a lovely idea, but they really really needed to be actual EC engineers involved in the development of this IC.

Excellent initial steps, but along way off usable for the most of us.

Look forwards to the future.

Am I just too stupid to find it or did they really not publish a proper datasheet for their controller?

Stuff like pinout/alternate functions, needed voltages, clocking and exact features of the peripherals are usually described in the datasheet. How can you decide if this controller would work for you without this information?

They did not mention a UART peripheral. Is it missing?

as far as I can see: yes the uart is missing.

Agree. At some point, they need to provide more information (I sent an email question on the Crowd Supply page). I also looked at the HDL source. Doesn’t appear to include a UART (although it also has 4 KB SRAM instead of the 8 KB the Crowd Supply page specifies).

I just got this reply:

Yes, it will have UART. We missed to include that in the specs.

A datasheet of the current fabricated micro will be include it in an update. However, since the offered micro in the campaign would be different than the current tested chip, a datasheet would be delivered after testing the v.2 parts.

The datasheet should be for the offered part.

I guess most parts for this are already designed and fixed, like pinouts, alternate functions and a detailed featureset for the peripherals (e.g. does the timer have capture/compare, does this work for rising or falling edge or rising and falling edge, what kind of pwm modes work with the timer and so on). This stuff should be published before the campaign ends.

Some stuff will probably only be available once silicon is available, like exact power consumption. This could be marked with “TBD”, like it is common in early datasheets from big vendors too.

From the documentation that I’ve seen, there is for “small hobbyists” not much to be gained in participating in this. If you participate in a $300 3D printer, you’d get that 3D printer. Now you get a $0.50 chip (comparable to an STM32F030 (minus some flash, plus some speed)) for $49 if you buy one, or $150 if you buy five. (OK, that includes the “development board”. For the STM you’d get those for $10 for a nucleo or $ <20 for a discovery board).

I don't see too many people investing in this just because they believe in Open Source.

Note that there is also an Open Source core in the Navspark. Not sure if it was "spark" or something else.

Hi rewolff. Thanks for the comments. Mask set cost and testing is expensive. If we can assure a more than million market, chip cost will be around 1USD. We are an organic startup, not a big company that can store million of dollars in stock waiting to be consumed. We believe things are going to change faster but for that we need to validate that market is there and for that reason things are expensive. Trust me, the campaign is not for profit at all!

hi elkim, i’m guessing you’re one of the people on the campaign, from your answer. hi, i’m luke leighton (lkcl) – i’ve just run a successful crowd-funding campaign with crowdsupply as well (EOMA68). i found as well that people try to make a comparison between “highly optimised mass-volume pricing” and “crowd-funding campaign with NREs to cove and a small volume target”. hilarious to find people comparing the assembled laptop prototype to a macbook pro for example. you can find the way that i answered this by looking at some of the comments, but you seem to be doing okay :)

aside from that, i wanted you to know that sadly i will not be using this chip that you are designing in any of the libre projects that i’m doing. the reasons: i need a 64-pin chip, i need on-board flash, i need a simple single 3.3v supply and i need RTC functionality. you should have received my comments via joshua or fred from last night by now: get in touch and i can help you to do a decent design. right now, this IC is ok for hobbyists but that’s about it. if you’re going to spend a ton of money on actually getting a chip done, why not consider doing it right first time?

Hi, thanks for your input. You have a point. Comparing is the issue. $500k for a microcontroller free (as speech) is quite low compared against about $50k-to-$100k daily spend by teams getting chips designed. The ton of money is not going to be spend in people is mostly foundry costs. A single supply it might happen, we are working on it to get a regulator for the 1.2V core without need of two supplies. However if open up a chip in check it out you will see some free pads (for testing purpose), those are different voltage rails with a LDO onchip. We are being transparent and saying each detail.

RTC functionality, it might happen too but it takes a two or three spins to get there. This is a start, it might no be the final chip for a fancy app, but it might be a chip to know chip details and overall: understand a lot of things. Doing right first time sounds like Greek mythology. We are trying but semiconductor history tells you how complex is this. We are putting circuits together, circuits that we know and circuits where our experience give us confidence, doing right first time for us is saying what we are capable of in the time range with limited resources. Give us some love, it is just 5 bucks!

perhaps there are niche markets, like cell phones without “Hydra on trusted platform, SMM, TrustZone” backdoors?

Did they share anywhere what kind of process they are using? 180nm?

130nm GP CMOS

Thanks for the comment. We’re using 130nm.

Excellent work, I hope they will be fully successful eventually. For once we might have an arhitecture that will not just be “obsoleted” at the manufacturer’s whim.

Where can we find more details about the supported ISA of this chip? just telling it’s a 32-bit RISCV is not enough.

After browsing through their github a bit, I think it’s RV32IM

Plus some custom extensions for interrupt handling

Thanks BaoBrien. You are right, RV32IM + interruptions

Check more info at https://riscv.org/specifications/

I guess so, I wouldn’t expect for it to be a RV32G. A little too pricy for me…

I want to help them but $50 for one chip is too much. For the campaign, I’d like to pay $10 and get it as a large QFP that I can actually solder.

Economies of scale… the price will come down eventually if it succeeds. I do lament the choice of QFP though. Tried one last weekend, and even with a DIP→QFP adapter, it was a pain in the arse and I still have no faith in the connection.

QFN has been chosen to get lesser power/signal integrity issues when running at 200MHz. QFP and even DIP for low freq. apps might be an option if campaign exceeds some numbers. Keep tuned.

dont be a grupy old fart, buy hotair station, even shitty $30 ebay special is fine. SMD is like lego compared to DIP being Erector Set.

Soldering QFN takes 5 seconds – put solder on all pads (too much/uneven is perfectly fine), shove your chip in place and push it into the board while heating to squeeze excess solder, swipe around the chip with soldering iron to pick up extra solder balls formed from the squeezed solder and .. congratulation you are done.

You can back the project with 199 and get a development board and 15 chips, that counts to me as 10$ per chip for small quantity. In fact from the board+5 chips to the board+15 chips they are only asking 5$ for every additional chip. Maybe they could make another option for a higher number of chips (without board) and claim a lower price per chip. I agree that one chip for 49$ doesn’t make much sense except as a collector item or to help fund the project. If you want it to develop a board you would like at least a few chips and the development will cost you much more money anyway.

Are these guys backed by a university? I’m wondering specifically where they are getting the EDA tools, since a back-end flow would cost more than the campaign amount.

We will be paying monthly license seats for specific tools once we get backed.

This would be an interesting thing to talk about when you are writing your updates.

This campaign just has “FAIL” written all over it. “Our chip is open and can be improved!” And who’s going to actually spend the money to spool up a new chip run, particularly after the initial batch is so expensive as to be laughable? People will say “well, the economies of scale will kick in”. Sure, but why would anyone want to chase a slowly falling price point when they can buy chips from a dozen other manufacturers for less than a dollar that covers a range of needs already? The one selling point they have: “it’s open!” is meaningless to the people who use dev boards based on them.

It is all about an endeavor. We are betting in the fact that RISCV is a growing community and that possibly will take over some ARM market in the 5-10yrs horizon. You might be the first on getting hands on a chip with an architecture that might be ubiquitous in the future. You might the first to show people around that this is going to be the right/wrong path. Exploring, we say. We humans love challenges and new ventures. It is just a different point, yours is valid too.

You are right, this is not a campaign for people who want a cheap Arduino board. This is a campaign for people who want a development board to write RISC-V software running on an ASIC for the first time (not emulation or fpga), or for people who want to develop hardware with the, probably, first RISC-V microcontroller. Sure 49$ is ridiculous for a single chip, but 199$ for board and 15 chips start to make a lot of sense. Sure small cortex-m0+ microcontrollers for less than 1$ exist, but most are in the 2-5$ range for small quantities. Do you really expected a small batch of new ASICs from a startup in a crowdfunding campaign to be in the bottom end of the microcontroller market price? That is only done by a “dozen” big companies manufacturing millions of chips and whose development and licencing costs are already recovered. It’s strange to me that people don’t see risk and a year and a half wait as the biggest issues.

i think his point is that this isn’t a commercially viable product at the 5usd mark and he would be right. yes low volume many chips in the m0 series are of similar pricing, but for commercial entities that price can be quite bit lower, something this chip cant do yet, hell this chip costs more at its cheapest tier than many commercial chips do on their most expensive.

without large scale use it might be difficult to actually keep developing, it costs money, hopefully there will be enough interested people for that to be a non issue.

Exactly. I like this project because I can have a real RISC-V chip to test and develop software for. C++ and Javascript emulations are nice but this chip is a real thing with real physical behavior.

I urge the Open-V developers: Please follow the KISS principle. Keep everything as simple and stupid as possible Don’t include internal flash storage in the first batch. You can do it later. EEPROM is ok for the first batch. Putting too much stuff into the first batch is too risky, and it could become a very disappointing experience.

Like the other commenters, this isnt for arduino fanboys/girls. if your intrested into the RISCV portion, than this is the first moment to get your hands dirty with the real metal. FPGA’s arent cheap and im thinking of a group buy. Im so hoping a more faster CPU will come out of this to use as a regular pc… probably wrong target with this setup but nomore hiden mcu that can phone home.

Also hope just like cheap china pcb makers, china will alow us to fab our own IC’s soon. these are the first steps. remember the arduino costing 40 coins? this aint about that yet, its about a full known, opensource ic, isa… whatver.

Will just the RTL be open sourced, or will the analog components (PLL/ADC/DAC/padring) also be available? Much of the cost of silicon is for IP like this, so open sourcing these macros could be very useful.

Analog blocks will be open too. Schematics and layout.

Felicitaciones muchachos. Espero que sea un primer paso para que se termine el control de la IP en manos de tan pocos.

“Congratulations guys. I hope it is a first step to end the control of the IP in the hands of so few.” – Frankenstein 2016

While I love the idea of this open source silicon (just supported you with 5 bucks), I cant stop to think how it will compete with big actors, with armies of microelectronic designers.

Thanks for your support. We have been part of different armies in the semiconductor industry, even the most popular ones selling to microcontroller-market. Armies are full of Captains and Generals. No many good soldiers and most of them are tired of the constant pushing without much innovation. There is the opportunity.

Why I won’t buy one:

I already have too many interesting things to play with, and not enough time for them.

And till 2018, when this chip arrives (or not), I’ll have gathered even more.

So it’s very likely, that this thing will just end up in the drawer, where it gathers dust forever.

And backed, I really like the idea of an open CPU that is actually available to buy. Yes it’s expensive and yes a cheap STM32F is more useful but that’s the cost of making a whole new IC.

I wonder if it’s possible to work with the CPU and some digital peripherals in an FPGA at the moment already?

The version 1 has been tested in a Artix-7 with a Nexys4 DDR board. The code and instructions can be found at https://github.com/onchipuis/mriscv_vivado

The version 2 RTL, the one of the campaign, might be released a couple of weeks before tapeout.

If even it is open source how anyone can use this,

maybe in some fpga implementation.

You don’t make his own microcontroller based on this

unless you robbery bank.

We may say about opensource if you can make it in home

which right now is impossible.

Sorry, what? dont you love opensource? do you compile everything yourself or are you just downloading precompiled binairies and feel great because you know you could checkout the sources anytime you want?

Dont get me wrong but everyone could compile not only the kernel, but also the OS other tools called Linux From Scratch, wonder if you are such a user. I think this is great, and yes, with alott of work and buying equipment, you could make this at home.

This comment probably doesnt make sense, but nobody got time for that right? you could make it at home, or with money send the plans to a chip fab just like your PCB… but you probably dont count that as opensource.

It’s a design, intellectual property. Like all open-source. That’s the point. No, you can’t make microchips without a fab, and you can’t make a shed without a hammer. That’s not the point.

Point is, before now there weren’t any free designs for CPUs, and now there are. From there, companies who do have fabs can create them, and maybe they will, the same way so many electronic gadgets these days run on Linux. In the future, maybe this one, slow, expensive chip will grow like Linux did. One day it might be extremely powerful, competitive with any other processor, but the design will be free.

As well as that, it’s a great start if you want your own custom CPU. You can add whichever specific features you want, on top of a working base design. That wasn’t there before. Of course, you still need the fab. That’s unavoidable til desktop nanotechnology, but it’s still a great step forwards. There might be cheap tablets or phones or desktops even, running on this in 10 years time.

You can’t criticise a microchip design because it’s impossible to make microchips in your garage. That doesn’t make any sense at all, as well as completely missing the point.

Absolutely, totally awesome. I was aware of LowRISC (I know, more ambitious and that), but you folks took me by surprise. You made my day.

And to all naysayers here: yes, the path to Free is tough. You’ll get cheaper chips if you can shoulder a 10^6 run upfront. You can make a Twitter if you can shoulder 10 years of losses (at how much? 2.6B?).

But those still trying are those who gave us gcc, Linux, FreeBSD, SSH, Apache, bash… You’re the ones making this world nice. Really: big thanks!

Thanks Tomás. It is quite tough but challenging. We, engineers, love challenges. BTW, we are committed with LowRISC team on designing the LPDDR3/4 beta PHYs.

maybe first riscV but not the first 32 bit risc http://hackaday.com/2014/08/07/parallax-propeller-1-goes-open-source/

A microcontroller is not just the RTL code. Peripherals are more expensive. We will be releasing analog and mixed signal circuitry. I would say RTL is just about 10% of the work. Parallax just released the RTL core for FPGA!

BTW, we are working to get PHYs for LOWRISC, yes, our own IP. We would pass 100% if you are seriously about getting hands in big pockets, sign an NDA with the foundry and tapeout chips, we will do it, that is the point. Call it 97% to the general public, which is enough to get a new paradigm rolling or maybe you think an arduino buyer will need the ESD details to pay a tapeout run? I wish I had something like this during my undergrad years to compare real analog against chapter books from Razavi’s book.

Nice input Mattaw. By the way you write, I am pretty sure we met before, SouthH….

Unfortunately for you, we have our own IP. We have developed and tested our own Std Cell library completely working in a commercial digital flow. All analog parts are our own designs. ESD cells are not, we will not release this, it is not ours but we can illustrate on this, even point out good papers. Devices are not restricted if you are not using fancy ones, such as varactors and so on. So Mattaw, you are right on Layout. We would not release layout databases, we will release GDS after using a converted version to Magic. You remind me IBM and Sun Microsystems when they were fighting BSD. Don’t bullxxxx, it is time to give thanks, Happy Thanksgiving!

I don’t understand the point of this. Sure, with open source software you can modify code to more closely fit your needs. With hardware, you can chop and change as you see fit. But silicon? I don’t see it as practical in the slightest.

Maybe 10 years ago this would have been feasible. But now, the market is locked up.

Here is a talk about RISK-V from MeetBSD 2016. https://youtu.be/QTYiH1Y5UV0

Not this implementation but good for a bit of background.