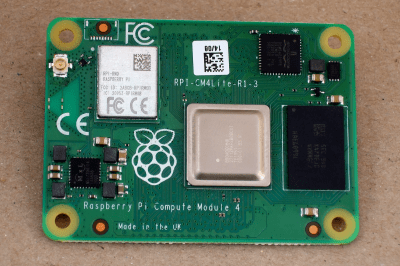

The brand new Raspberry Pi Compute Module 4 (CM4) was just released! Surprised? Nope, and we’re not either — the Raspberry Pi Foundation had hinted that it was going to release a compute module for the 4-series for a long while.

The form factor got a total overhaul, but there’s bigger changes in this little beastie than are visible at first glance, and we’re going to walk you through most of them. The foremost bonuses are the easy implementation of PCIe and NVMe, making it possible to get data in and out of SSDs ridiculously fast. Combined with optional WiFi/Bluetooth and easily designed Gigabit Ethernet, the CM4 is a connectivity monster.

One of the classic want-to-build-it-with-a-Pi projects is the ultra-fast home NAS. The CM4 makes this finally possible.

If you don’t know the compute modules, they are stripped-down versions of what you probably think of as a Raspberry Pi, which is officially known as the “Model B” form-factor. Aimed at commercial applications, the compute modules lack many of the creature comforts of their bigger siblings, but they trade those for flexibility in design and allow for some extra functionality.

If you don’t know the compute modules, they are stripped-down versions of what you probably think of as a Raspberry Pi, which is officially known as the “Model B” form-factor. Aimed at commercial applications, the compute modules lack many of the creature comforts of their bigger siblings, but they trade those for flexibility in design and allow for some extra functionality.

The compute modules aren’t exactly beginner friendly, but we’re positively impressed by how far Team Raspberry has been able to make this module accessible to the intermediate hacker. Most of this is down to the open design of the IO Breakout board that also got released today. With completely open KiCAD design files, if you can edit and order a PCB, and then reflow-solder what arrives in the mail, you can design for the CM4. The benefit is a lighter, cheaper, and yet significantly more customizable platform that packs the power of the Raspberry Pi 4 into a low-profile 40 mm x 55 mm package.

So let’s see what’s new, and then look a little bit into what is necessary to incorporate a compute module into your own design.

So Long, SO-DIMM

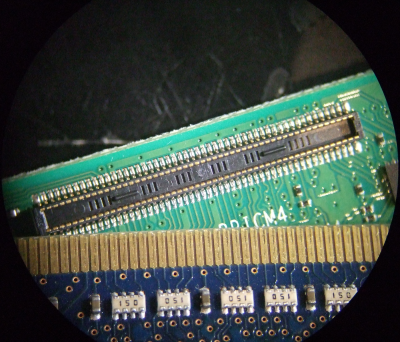

The biggest shocker with the CM4 is the new connector. Ever since the first Raspberry Pi got its compute module, they have come with 200-pin SO-DIMM connectors, just like DDR2 memory boards for a laptop. The CM4 changes that, opting for two high-speed, high-density 100-pin mezzanine connectors. Breaking with tradition is traumatic, and we know that some of you will be left with a closet-full of SO-DIMM sockets, but they did it for a good reason.

The system-on-a-chip (SOC) that the Pi 4 family uses, the Broadcom BCM2711, brought a lot more peripheral capability to the party (PDF). As a result of this, the Pi 4 Model B picked up a second HDMI connector, USB 3.0, and Gigabit Ethernet. But it was capable of even more! For instance, it wasn’t long before enterprising hackers realized that the USB 3.0 was on a PCIe bus and swapped out the USB 3.0 for PCIe. This was doable, but difficult, with some intricate on-board rework.

The system-on-a-chip (SOC) that the Pi 4 family uses, the Broadcom BCM2711, brought a lot more peripheral capability to the party (PDF). As a result of this, the Pi 4 Model B picked up a second HDMI connector, USB 3.0, and Gigabit Ethernet. But it was capable of even more! For instance, it wasn’t long before enterprising hackers realized that the USB 3.0 was on a PCIe bus and swapped out the USB 3.0 for PCIe. This was doable, but difficult, with some intricate on-board rework.

The compute modules exist to make all of the SOC’s capabilities easily available to the designer. Packing PCIe alongside twin HDMI and other high-speed peripherals into the old SO-DIMM connector was just not possible, and this was hinted at by the Raspberry engineers in the summer. Hence the new connectors: Hirose DF40C-100DS-0.4V if you’re already getting itchy board-design fingers.

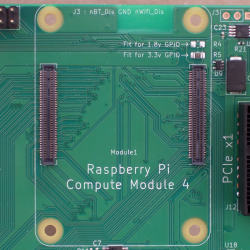

With two mezzanine connectors in place of a single SO-DIMM, the CM4 design implements a nice split between the low-speed and high-speed peripherals. One side has the traditional Raspberry Pi GPIOs, power, SD card interface, and Ethernet. The other side takes care of PCIe, USB, HDMI, and the MIPI CSI camera and DSI display lines, two of each. On one hand, that means you have a lot more high speed IO to play with, and on the other, you could get by with a simple one-connector design if you didn’t need any of the high-speed stuff.

With two mezzanine connectors in place of a single SO-DIMM, the CM4 design implements a nice split between the low-speed and high-speed peripherals. One side has the traditional Raspberry Pi GPIOs, power, SD card interface, and Ethernet. The other side takes care of PCIe, USB, HDMI, and the MIPI CSI camera and DSI display lines, two of each. On one hand, that means you have a lot more high speed IO to play with, and on the other, you could get by with a simple one-connector design if you didn’t need any of the high-speed stuff.

The new connectors also allow a smaller footprint for the module, and lower board height and weight when it’s installed in your device. They implement a better separation of the high-speed and low-speed domains, so they’ll be easier to lay out. Heck, they even cost less for the pair than the old SO-DIMM socket did. And given that this is the tradeoff for PCIe, we’re not lamenting the change in the slightest.

32 Flavors: Buy Just the Pi You Need

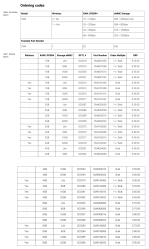

The CM3 had more ordering options than the CM2, and the Pi 4 Model B had more memory configuration options than the Pi 3 Model B. But the CM4 takes the cake. There are 32 different varieties, at correspondingly different prices. Why? There are four tiers of RAM, four tiers of on-board eMMC storage, and the optional wireless module. (4 x 4 x 2 = 32.) Let’s start off with the base model: a CM4 with no wireless, 1 GB of RAM, and no eMMC. That’ll cost you $25.

For the rest of the options, it’s like pizza toppings. An extra $5 gets you wireless. For $5 per tier, you can add 8 GB, 16 GB, or 32 GB of eMMC. To get a board with 2 GB of RAM costs $5, 4 GB costs $20, and 8 GB costs $45.

A quick quiz: how much is a CM4 Lite (no eMMC) with WiFi and 4 GB of RAM? We get $50. CM4 with wireless, a beefy 32 GB eMMC, and 2 GB RAM? Also $50. A Pi with everything (wireless / 32 GB eMMC / 8 GB RAM)? $90.

Some possible configurations are listed in the datasheet as being “Bulk” while others as “1+/Bulk”, so it might be that they’re not all equally easily available to the smaller user. For instance, if you want wireless in quantity 1, you may be limited to 2 GB or 4 GB RAM configurations. All tiers of eMMC are equally available, however. Since this can all change depending on customer demand in the long run, you might want to check out the Raspberry Pi website for the latest.

Plus PCIe, Minus USB 3.0

Compared with the Pi 4 Model B, the CM4 is drastically more flexible. The headline difference is that the CM4 no longer dedicates the PCIe bus to USB 3.0. This choice made sense for a consumer-oriented board, but the CM4 is for designers. PCIe can be added very simply to a CM4 design: all you need is the right socket and 3.3 V and 12 V power rails. And this has even been tested with the newer NVMe solid-state drives. Raspberry engineer Dominic Plunkett told us that they were getting 390 MBytes/s write speed in the lab, which is pretty close to the theoretical maximum speed. You’re trading this for the USB 3.0 port of the Model B, but if what you’re after is fast SSD I/O, PCIe with NVMe is the cutting edge. Not bad for a single-board computer!

The Model B only has one two-lane MIPI CSI camera connector and one two-lane MIPI DSI display connector broken out. The CM4 allows two of each, enabling stereoscopic 3D imaging, for instance. (You could also do this with the the CM3+, but that’s old and busted as of right now.) Moreover, the Model B exposes only the two-lane versions of CSI and DSI, while the CM4 additionally gives you four-lane variants for higher bandwidth. Using these, you can get even higher performance out of the camera without resorting to external hardware. Want ultra-high frame rate or resolution video on DSI screens? CM4.

Even the optional WiFi/Bluetooth module is more flexible. In addition to the onboard PCB antenna, they’ve added a UFL connector for an external antenna, and both the internal and external antennas can be enabled or disabled from software as needed. This makes the CM4 the right choice for demanding WiFi applications, or simply for building inside a metal box. The Raspberry Pi Foundation will sell an antenna that’s FCC certified for use with the CM4, or you can bring your own but then it’s on you.

Even the optional WiFi/Bluetooth module is more flexible. In addition to the onboard PCB antenna, they’ve added a UFL connector for an external antenna, and both the internal and external antennas can be enabled or disabled from software as needed. This makes the CM4 the right choice for demanding WiFi applications, or simply for building inside a metal box. The Raspberry Pi Foundation will sell an antenna that’s FCC certified for use with the CM4, or you can bring your own but then it’s on you.

Last, the Ethernet chip got a tiny upgrade, to the BCM54210PE on the CM4. It’s still a Gigabit Ethernet PHY chip, but this one also supports IEEE 1588 Precision Time Protocol. If you need better-than-NTP time sync, you know what all of this means.

Open Questions

We noticed two things that made us curious while working over the CM4 datasheet with our fine-toothed comb.

First, it says that the CM4 is more efficient than the Model B, so it uses less power. But because it’s on a smaller board, it’s not passively heatsinked as well as the Model B, and it may still be more prone to throttling down the CPU speed to keep from overheating. There are no numbers available yet, but we’re going to get our hands on a Model B and put the two to a stress-test comparison soon. Stay tuned.

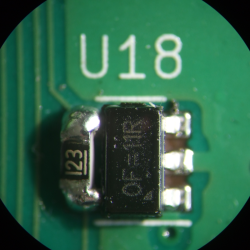

Second, there’s a tantalizing sentence about two analog inputs that were left over on the MXL7704 power-management IC, and you’re referred to the datasheet (PDF) for further study. They seem to be broken out in pins labelled AIN0 and AIN1 on the official IO board. Looks to us like the gauntlet has been thrown.

Finally, sometimes flexibility conflicts with ease-of-use. The Model B comes with a total of four USB ports: two USB 3.0 and two USB 2.0. USB 3.0 got axed, and the CM4 only has connections for one USB 2.0 port, because that’s what the Broadcom SOC supports natively. If you want more USB ports, you’ve got to build your own hub. That’s what they did on the Model B, and it’s also what they did on the CM4 IO demonstration board. And speaking of the IO board…

Getting Started: The IO Demo Board

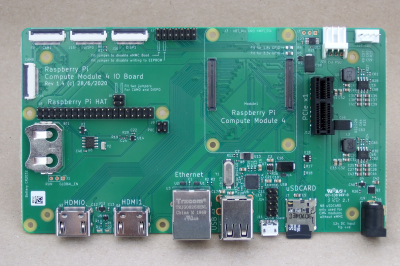

We got an IO board delivered along with our sample CM4. With solid documentation as well as KiCAD design files available, it’s basically a template for making your own CM4-based design. Have a look!

We’re impressed by how little is needed to get all of the functionality of the CM4 out into the real world. The HDMI ports are simply wired straight from connector to connector, as are the MIPI camera and display lines. Ethernet is implemented with power-over-Ethernet protection, but if you didn’t need that, you could just wire straight from the CM4 to the magnetics. (Or to an optical transceiver?) PCIe is similarly simple: outside of 3.3 V and 12 V power rails, everything is straight from the CM4 into the socket.

Indeed, the only parts of the IO board that look like they took any design work (no offense, RPi engineers!) are the USB 2.0 hub that allows up to four connections, which you can copy straight-up if you want a tested design, and the power supply that converts down from a 12 V barrel jack to 5 V for the CM4 and to 3.3 V for the PCIe connector. The SD card, to accomodate the no-eMMC “Lite” version of the CM4, has a high-side switch so that it can be turned off by the CM4 to save power when not in use. Everything else is simply wires.

But they’re not necessarily simple wires, and this is the one gotcha for people who haven’t designed high-speed boards. There are basically two classes of traces with which you need to be careful: 90 Ω differential pairs and 100 Ω differential pairs. The first group includes PCIe and USB, and within pair they need to be matched down to 0.15 mm, with 0.1 mm recommended for PCIe. 100 Ω pairs are specified for Ethernet, HDMI, and the MIPI CSI and DSI connections.

According to the datasheet, across-pair lengths are significantly less critical, but between two lines in a differential pair, it pays to match lengths. KiCAD does differential pairs since CERN added it in 2015, and Saturn PCB toolkit comes highly recommended for calculating impedance-controlled trace widths, but it’s Windows only. (You might be able to just crib the trace widths and separations off the IO board design and ignore this whole issue.)

Of course, you don’t need all of these high-speed peripherals unless you need them. You could run a CM4 server with eMMC and wireless using just the 5 V and GND pins, assuming you had a way to get the software into the eMMC in the first place. For the classic headless-Pi experience, you could wire up the GPIO and SD card lines as well, all without worrying about impedances. (Note that you could do this using only the low-speed mezzanine connector. Nice.)

But that’s not why you’re here. You want to turn the IO board reference design into that high-speed custom PCIe NAS, remember? Off you go! Just remember to design in plenty of status LEDs.

Wrapup

In conclusion, the CM4 is everything the Raspberry Pi 4 Model B is, except in a more flexible, less consumer-friendly package. It comes in 32 different varieties, and exposes some seriously high-end peripherals, which is all the more impressive for the low price tag. The real cost of admission is designing your own board to go along with it, but even that doesn’t look to be too bad with some help. We’re looking forward to see what you all do with it.

Cool stuff, maybe now I can finally get my old PineBook to actually run a desktop environment :D

the form-factor changed. Will it be compatible with your pinebook?

nothing that can’t be fixed with wires and hot glue.

What are the unpopulated pads on the top edge of the board? Next to an FCC logo

No clue. Looks like a socket footprint of some kind, though, no?

There seem to be 6 signals, and two grounds. One of the signals ends in a test point on the back, and another snakes off under the wireless unit’s can. It’s a 4-layer board, and the other four signals seem to go somewhere into the sandwich.

General location makes me think radio, but the fact that it’s routed around a fiducial makes me think unimportant. Well, that and it’s unpopulated after all. :)

Looks similar to a debugging port found on other Pis.

Its just a JTAG connector, for bringing up and debugging the board.

Please provide further clues for the quest.

That’s the VC6 jtag debug port. It’s unpopulated as there aren’t any tools to make use of it outside of Broadcom/RPi Foundation.

Looks like it might be for a threaded antenna mount like you would find on proper wifi hardware. Just speculation of course.

Looks like a Mini USB 8pin connector.

Would make sense for the flashing of the eMMC.

A lot of businesses will not only switch designs, they will opt for a board that will stay the same shape so they can still use their 1k+ boards on the shelf.

Unless they also produce the older version as well of course.

Me for one am happy I choose the nanopi neo for a product in the knowledge it will be produced for a while and has a “long term support” label, hinting on a timely notice of obsolence.

CM3+ still available, the CM4 available until at least 2028. Was not able to find an obsolescence statement for the Neo so cannot compare.

Now my only question is.

How many PCIe lanes does it have?

The datasheet though quickly answers this.

It has 1, and at PCIe 2.0 speeds.

Ie, only about 4 Gb/s, it’s fast, but not super impressive.

A SATA3 port is faster, by a lot. (SATA3 is 6 Gb/s (50% faster))

Thankfully, the chip used already has 1 Gb/s networking on board, so no need to spend our PCIe lane on that.

But I wouldn’t really consider this platform as a good base for an “ultra-fast home NAS.”

Considering that an old relic of a PC typically has 3-8 SATA ports, most being SATA3, and a smattering of PCIe lanes, some even 3.0 ones, so 10 Gb/s networking is an option. And then typically support for more than 8 GB or RAM, so ample space for caching.

If the CM4 had 4 PCIe lanes then it would be far more interesting from a NAS standpoint, or anything PCIe related to be fair.

Like I would happily trade that second HDMI port for a pair of PCIe 3.0 lanes. (The HDMI 2.0 port sends data at up to 18 Gb/s, and has 4 differential pairs, this could technically be used for two PCIe 4.0 lanes, if the PCIe controller can keep up that is, so 3.0 lanes are more realistic…)

Correction on the HDMI 2.0 statement:

HDMI 2.0 has 18 Gb/s combined bandwidth for it’s 3 data pairs. (the fourth pair is for the bus clock)

Ie, each pair is only sending data at 6 Gb/s, far from sufficient for the 16 Gb/s that PCIe 4.0 uses for its lanes.

Though, should be sufficient for SATA3, or if just slightly speed up could reach the 8 Gb/s that PCIe 3.0 uses. (If only there were a PCIe 2.5 that were 6 Gb/s, and a PCIe 3.5 for that matter at 12 Gb/s.)

This. It raised an eyebrow very high when the article basically started by claiming a classical Pi usage would be “ultra-fast home NAS”.

Folks, the BCM2711 is still something that’s optimized for set-top box style devices. No amount of marketing the CM as “embedded board for industrial applications” changes that. It’s really a poor fit for most applications that a raspberry pi is used for, and it’s a testament to the versatility of broadcom hardware that it’s still useful.

First of all, the previous few days, a new “oh, you want to put a Linux-capable computer in your embedded device” guide made its rounds, and it’s actually pretty good:

Second: there’s bigger fish than the RPi foundation if you want control/deeply embedded system-on-module:

https://jaycarlson.net/embedded-linux

For example, NXP has a [recommended vendor](https://www.variscite.com/products/system-on-module-som/?cpu_architecture=Cortex-A53%20/%20Krait&cores=Quad,Hexa&connectivity=PCI-Express) ; so do other vendors too.

I’m really failing to see the appeal of a compute module with a 4K-capable video output marketed towards deeply embedded applications (which typically means “headless”). Maybe I’m missing something, but:

You don’t gain “mechanical ease” by using this the CM4 – it exports high-speed signals, and hence, a motherboard using these would need high-speed design. At which point we’re leaving beginner territory (that’s OK, not marketed towards beginners), and at which point the things that “usual” board / SoC vendors offer become real cost-savers.

You know what, when I buy an NXP SoC directly and drop it on a board, I get an IDE that allows me to assign pin functions as I want them. I get direct access to support fora (I challenge you to do that at Broadcom). What I don’t get is Raspbian, which personally isn’t a big deal. I’d much rather have a working Yocto BSP or Buildroot integration, anyway.

Power consumption of the Pi 4B is better than it’s ever been (so I presume the CM4 is roughly the same), which means it’s still the most power-hungry Pi ever to exist, and among the least power-efficient ARM SBCs to be designed, but it’s finally in the “usual ballpark for devices of this computational power”, which previously wasn’t the case (due to earlier RPi being slow and still power-hungry).

I love the RPi foundation, and what it has achieved for pervasive homebrew computation. I don’t think them trying to diffuse into industrial usage is a good idea overall, but that’s their business decision to make. For some reason, modern industrial higher-end SoM tend to integrate things like a Cortex-M4 core alongside with their Cortex-A cores – simply because you rarely need only high, but non-deterministic throughput, but in control applications often need something that can react within a defined number of nanoseconds. The BCM2711 doesn’t have such functionality. It doesn’t have great PCIe or Networking (hint: check the “Spear MX8” board’s datasheet to compare.), ADCs or industry-standard buses (CAN? any other field busses?).

The RPi foundation is pushing consumer multimedia hardware into critical industrial applications. I hope it works out well.

RPF(T) sell 50% of their product in to industrial applications and have done for years (that’s millions per year). And some of your comments on the SoC itself are a little ‘off the markl’

Would be helpful for you to tell us which comments on the SoC are a little ‘off the mark’.

I think I agree with everything he said – the main problem with A-series arms in industrial service is the non-deterministic interrupt latency. Next is pipelines, out-of-order execution, speculative execution, cache coherency.

When that pulse to the output pin really, absolutely positively has to arrive on time to stimulate the heart tissue so the beat is on-the-beat, you should be using a cortex-M series core.

A Raspberry Pi or anything that runs a full on Kernel shouldn’t be trusted with real time control.

It can be supervising a system, handle larger system states, do logging, and put for updates to when stuff should change.

But actual control handling real world interactions should indeed be handled by a processor that has a fixed cycles/instruction (at the very least for a given instruction), but also no out of order execution, no speculative execution, and preferably not have cache either. (since cache misses can lead to latency spikes and thereby non deterministic timing.)

I generally prefer using smaller microcontrollers, but a cortex-M can be decent if more number crunching grunt is needed, of if one needs to handle larger amounts of data/bandwidth. (A PIC micro is kinda weak in that regard.)

Though, at some points, it can even be nice to have dedicated logic/hardware for a function, though this has its own set of issues.

If you want you can run a rtos on one of the cores giving you much better interrupt latency go for it. To be honest if you want to respond very quickly (IE. Nanoseconds) to something then you can populate the logic directly on your io board / use a small micro controller.

For our application, we can make a “specialized” device that has a bright sunlight readable screen, custom button functions, and all sorts of other cool things, *and* is 100% bit compatible with an RPi that Jane Sixpack can buy off the shelf and program. So Jane can play around with the vanilla RPi then turn around and target our device with a small change to `boot/config.txt`.

http://www.airball.aero/2018/07/introducing-new-and-improved-fully.html

What are some SoCs and boards you recommend checking out? I’ve been looking into some of the options out there for NAS and router applications. I’ve been swinging back to x86 for the main reason that updates for things like pfSense and Unraid can be used directly without waiting for any device specific porting as is typical with an embedded platform. This also means I can stay up to date long after the hardware is EOLed by the manufacturer too.

The Pi foundations seems to be moving in that direction and are getting there though the the Pi hardware still isn’t a great fit for a router or NAS right now. Are there other embedded platforms that are more capable in these roles and allow for direct updates without the device manufacturer’s blessing?

Your numbers are incorrect. PCIe 2.0 is 5Gbit/s and it’s using same 8b10b encoding like SATA3, therefore SATA is 20% faster on the transfer layer. But SATA3 has approx double protocol overhead compared to PCIe, therefore you will get 550MByte/s vs 500MByte/s during a sequential file transfert. It is only 10% advantage in speed, but it lacks the hardware flexibility.

My main point where though in regards to the “ultra-fast home NAS.” that the article suggested as a valid application for the CM4. And honestly, since the device doesn’t get up the even the speed of a single SATA3 port, it is going to be very far away from “ultra-fast home NAS.” territory, even with NVMe storage…

Though, would personally find a device with more PCIe lanes as more interesting, even if it is only PCIe 2.0 lanes. Since PCIe add in cards do provide a lot of flexibility.

I think its pretty fair to call it a fast home NAS.. as most home NAS’s are really really cripplingly slow in comparison to what the Pi4 can do (and if accessing over wifi that will be the limiting factor anyway). Won’t ever be the fastest NAS possible – but as a balance of power consumption and speed with greater control of its features and hardware than off the shelf its a fair use case.

I actually still use a Pi1 as my NAS, being more than fast enough for the 3 people that tend to use it, (that same Pi also runs a few other services as well) and it works just fine. It consumes in a year less power than the NAS it replaced did in a month while being about as performant, and way way less than using some old ATX PC. Though a real PC can also run the additional services so can be a very valid choice.

I don’t see it being the Pi4’s best use.. But its a perfectly valid use. For me with its relatively capable processor and ram, with good screen options I can see many embedded uses – driving your AR headset, a infotainment system that doesn’t compromise your car’s security and safety.

I use my normal Pi4 to run virtual machines sometimes. It has become my always on music/video and test bed. The workstation still blows it away performance wise of course, but the Pi4 does all my lighter load requirements while being portable and energy efficient (i’ve got mine mounted inside one of those solid smartphone cardboard boxes with a large heat sink I had laying around (from a linear regulator I think) So I can just unplug it close the box fully and take it – its way more potent than my laptops). My workstation on the other hand can’t idle under 100W and weighs at least 15KG thanks largely to all the cooling high power CPU and GPU require…

A raspbery pi will surely make for an adequate NAS server in most cases.

But I don’t agree with the article’s “ultra high performance NAS”, since that contains the words “ultra” and “high performance”. If it were just “NAS” then it would be fine, or even “high performance NAS” would be reasonable, since it does run 1 Gb/s without major issues. But adding “Ultra” makes me at least ask for 10 Gb/s networking at the very least.

And yes.

A Pi makes for a wonderful 24/7 system. Use one myself to run various internet facing tasks.

It has good performance, lower power consumption, and does an admirable job. But obviously isn’t replacing a proper work station anytime soon.

I setup a video server with a 32 bit HP thin client and its matching PCIe x4 expansion addon. Found a 16 gigabyte SATA SSD that would physically fit and maxed out its RAM. Plugged an eSATA card into the expansion chassis and an external 500 gig drive into that. With the 32 bit version of Open Media Vault 5 installed it uses just a few watts. Wouldn’t be surprised if the hard drive uses most of the power when it’s spinning. I may change it to a PCIe NVME adapter so it will be a one box thing. I’ve also thought about getting a second expansion chassis to gut and attach then switch to a SATA car with internal ports and put drives in the 2nd expansion.

For this use all it has to do is make videos available on my LAN via DLNA so Smart TVs can use their built in software to play them, and it works fine for that.

When can we expect the next Zero?

the ususal answer to that question from Eben is “when they find a well priced SoC that can have a bigger PoP memory die”

and never forget, on Rpi you are a back seat driver. Real OS runs in graphics core.

>Real OS runs in graphics core.

Can you explain a bit further? I’m not well acquainted with this matter.

VideoCore starts booting the system and has full access to RAM and peripherials. ARM core is secondary.

binary blob for decent graphics not open source frome broadcom….

Rubbish. And a for the form factor – what would be the point of a CM4 that didn’t expose all the feature set? Not possible to do that without a connector change.

Oh yeah, and Real(time) OS runs in the wi-fi board too ;-)

Well yes, there is firmware running on VPU but it does less and less things than before. Most stuff is moving to ARM side (3d, hevc, hdmi, dsi,…). closed firmare is mostly just camera older codecs and thermal throttling, and indeed the boot procedure until ARM is powered on.

So it seems that the USB 2.0 ports on the demo board are provided via the single USB 2.0 OTG port that is connected to the USB-C connector on the current Pi 4 boards. Which means you choose between USB 2 device or USB 2 host, and USB 3 host or PCIe.

That’s a bit disappointing!

Well, that’s the problem with the SoC.

If you want a bit more PCIe or PCIe attached peripherals, wait for someone to make a carrier board with a PCIe switch on it. You can get PCIe x1 to many x1 switches, which would be ideal. Sure, you have a bottleneck to the Pi, but you can’t help that.

Maybe the next Pi SoC will have a PCIe 3 x1 port, or an x2 even. But that’s probably next year at the earliest.

At least this board is slim. Could make some of those chunky Pi laptops, etc, a lot slimmer.

Hand soldering those two connectors within tolerance to get them both to perfectly align with the compute module is going to be a total nightmare!

I’m thinking hand-soldering is pretty much out, here. You really want to use just the right footprints and let the reflow surface tension self-alignment work its magic.

Depends on your desperation level… I have 3d printed an alignment bracket for _smaller_ connectors than that before, that _sort of_ worked…

Do-able? YES!

Should you? Hell no! But I was desperate.

They’re totally free floating. Which means now the problem is placing the connector and moving it to the reflow area. Yeah, you could try using a hot air gun, but with soft plastic like these…

It’s *really* frustrating they didn’t pick a connector with alignment pins. That’s *really* frustrating.

Order a board for 25€ and use it as a aligment tool.

Use dremel to get close to the connector on some areas and handsolder parts of the connector to the board.

Remove the board and solder the rest of the connector. First step you dont need to handle bridges, solve them in step 2.

I think with a microscope the connector is not hard to solder aligned.

We soldered one side on, put the module in with the other connector fitted and then soldered it down. Worked a treat

Superglue…

Place the connector in the module, put a small amount of superglue to the bottom of the connector, place it to the board, remove the CM. Connector stays in the perfect place and you can solder it in place.

Might work. Those things are on pretty tight, though. I had to grab a plastic scalpel handle to wedge underneath to pull it out.

I would personally worry about getting super glue residue on the pins themselves as it squeezes out.

Not to mention that the connecters tends to hold together rather strongly.

Though, no need to actually seat the connector.

And if one has a laser cutter on hand, then one can always cut out a jig that holds the ends of the connector. (Likely blocking the outermost pins.) So that one can properly solder the middle pins on both sides before removing the jig and soldering the rest.

Will though require that one has a decent laser cutter that is trimmed in, but that isn’t too hard to fiddle with to be fair. And one can just as well use a milling machine, 3D printer, or even a steady hand and some time.

A well made jig is the solution to most manufacturing problems as far as alignment is concerned.

Soldering those are a walk in the park. Many of these connectors have alignment pins that push through the PCB.

And yet, these don’t, sadly.

They’ve got a wide self-alignment range (0.33 m). Nightmare is stretching it. The pins themselves have +/-0.08 mm play horizontally, so that’s not a problem. *Vertical* is more of a problem (there’s 0.4 mm play there), but it’s not *that* bad.

wow 0.3m, that is great! You can just set the board in the rough vicinity of the breakout :)

Hirose DF40 is the same connector series used on the Intel Edison that was despised by many.

I have hand soldered these exact connectors before and its not the most fun thing I have done. I think they are .3mm pitch. And yeah, you are going to have to have a fixture for alignment, they are not forgiving.

It seems very tempting now to design a small, cheap(-ish) Raspberry Laptop with a 13″ Thinkpad keyboard, 20 hour battery life, Gigabit LAN and a NVMe SSD! Boy, I love these times we live in :)

NVMe is kinda pointless when all you have is 1x PCIe 2.0 and you’d probably want to use that for the missing USB3.0 ports…

Linux certainly supports PCIe switches. So a simple one x1 to four x1 switch would give you extra lanes of PCIe and you could hang off USB 3 and NVMe. Granted, you are sharing one pipes worth of bandwidth, but hey, we lived with USB 2.0 for a long time!

Yeah, why?

My desktop PC has every single external device hanging off a single USB 2.0 hub. Keyboard, mouse, bluetooth for headphones, usb audio mixer, midi controller, *webcam*… no issues.

And on the hypothetical CM-laptop – both webcams are on the CSI bus, the keyboard and trackpad could easily be GPIO or even serial, Wifi and Bluetooth are on SPI/UART, ethernet has a dedicated bus, audio can be exposed over SPI or just break it out from a HDMI port with the video for the LCD…

I don’t have any idea why I would so desperately need USB 3 on this device. Heck, I could survive without USB at all.

And hell, even forget USB-C power – just charge the thing over PoE to boot.

The new form factor dashes hopes of a CM4 version of a TuringPi. I am disappointed. :(

Maybe this announcement will make you less dissapointed

https://twitter.com/turingpi/status/1318109669752274947

“Wondering how are we going to make it with the new form factor? We are going to announce the Turing Pi V2 soon. And yes, V2 is going to come in a case. Stay tuned!”

See the full announcement at https://turingpi.com/turing-pi-2-announcement/.

Its https://saturnpcb.com/pcb_toolkit/

not http://saturnpcb.com/pcb_toolkit.htm

Thanks, fixed!

WTF, Pi Foundation: according to the datasheet the operating temp range is *worse*? 0 to 85? Are you freaking kidding me?

F’crying out loud, a common -40 to +85 compute module w/PCIe would be stupid useful. Why??

Why would you want -40 degrees Fahrenheit?

Because we live on a planet where stuff routinely goes below 32F?

Conveniently -40f is also -40c

Anyhow, some reasons off the top of my head, any of these applications could be used in areas with cold winters:

Datalogging or automation/control on industrial machinery

Anything automotive

Agricultural monitoring/control (In the USA pigs/hogs are grown indoors year round, but you might need some equipment capable of functioning if the heater was down, or to be stored in an area not climate controlled)

I’m sure there are more.

To be clear the operating temp for the CM4 is 0 to +85. To me, 0 to +85C means “indoors only.” I don’t think there’s any place in the US that doesn’t have *some* part of it that gets below 0 C outdoors relatively often (although obviously on Hawaii, no one *lives* in those areas).

Outdoor applications

Industrial cold storage applications

If you need something with industrial temperature ratings then buy one. Does no one remember the reason why the Pi was created? It was meant to be built as cheaply as possible for students to learn. It was never meant for speed.

Indeed, Students learn on the Pi platform and then get hired for bottom dollar in industry and tasked to design a one off or low qty solution… You bet they’re using a Pi :) Sometimes they will go to the effort to use a CM, damn low cost students… Or more realistically they mention the price of the pi and the execs are sold! – You should see the qty of Arduinos that have been cobbled to replace Siemens PLC systems at my local port :(

I can’t wait to meet all those students that are going to learn to solder 0.3mm-pitch connectors so that they can run Scratch on their Pi4 Compute Module.

Forget the “for educational purposes” thing, for years it’s been very clear that is no longer the main focus.

Uh, I do, which is why I’m frustrated these aren’t. I can’t tell you how many people want to throw Raspberry Pis on stuff because that’s what every damn project uses, and then wonder why I use “niche” stuff like a BeagleBone Black because it actually meets spec.

IF you really need that degree of cold and the Pi doesn’t self heat into its operating window you can always add a heater. Not like its unusual for electronics meant to work in harsh environments to come with their own climate controlled enclosure. (The pi4 puts out a fair bit of heat from that little die, I expect this will be exactly the same so keeping it in the operating window is probably just put it in a moderately well insulated box)

We are looking in to those figures- the datasheet will be updated in due course.

That’s fantastic! I was really hopeful when I saw that there’s a no eMMC option and the LPDDR4 is rated down to -40. I’d be perfectly happy with a solution rated to -40 without eMMC, that’s understandable and easily worked around.

“In conclusion, the CM4 is everything the Raspberry Pi 4 Model B is, except in a more flexible, less consumer-friendly package.”

Uh… Not true. CMx modules have extended temp ranges, unlike ALL of the other RPI product line. Most RPI users forget / dont even know this any yet they still throw them in hot and cold environments. They will fail when you do this.

It’d be nice if this were true for the CM4, but check the datasheet. You gain a bit on the higher end (15C) but the low-end temp’s still the same. The older CMs were sadly also only a little below 0 (-20 to +85, if memory serves), and annoyingly it’s the two components that likely *will* misbehave out of their temperature range (the eMMC/LPDDR2, both of which have internal behavior that’s temperature-compensated.

“dont even know this any yet they still throw them in hot and cold environments. They will fail when you do this.”

The really annoying cases are when people throw the “but… but… I’ve thrown my Raspberry Pi in liquid nitrogen, and it’s fine!” Sure. Might be, for a while. There’s a difference between operating *one* thing outside its operating range for a short time and wanting to operate *hundreds* of them for extended times.

A base board that connects the PCIe to a quad Gigabit NIC would make a nice router. Loads of compute power to run VPNs and plenty of RAM to implement VMs/containers for sophisticated network setups that would normally take multiple routers.

Yes, I had the exact same thought when I read this.

Indeed, I really like this idea… And now I need yet another Pi and a reflow soldering option.. Damn you!

Heck being potent enough can probably run a video chat server while still doing all that. Which in the current lockdown type situations might be a real winner (if you object to all the big data type corps so want your own system at least).

Or just get a $5 riser card off eBay and a PCIe quad ethernet adapter?

Exactly my thought. Over the years many people proposed RasPi routers, the idea always made me cringe because the hardware really wasn’t suitable, cramming Ethernet through the USB bus. With the Pi 4, we finally got proper Ethernet, and now with this module the potential for a really good router set-up.

What’s really exciting here for my purposes is that thanks to NEON SIMD instructions in the Cortex A72, the Pi 4 can push Wireguard encryption at full gigabit line speed.

How critical is the stackup here for the impedance matching on the PCI-E.

I suspect that could be a bit of a barrier to making our own boards here in some situations, since I haven’t seen too many of the “lower cost” prototype board house options offer controlled impedance. Maybe they do and I’m just not looking hard enough. :)

Cheaper board houses do have impedance options available, the JLCPCB-offered controlled impedance offerings don’t even add any extra cost when you order it with a 4-layer board, if I’m not mistaken.

I guess I was just not looking hard enough then. :) To be honest, the highest speed stuff I usually do is USB 2.0, so I can get away without too much care on prototypes.

The biggest issue with controlled impedance is if you do an interior pair, in edge (or worse, broad) coupled stripline. Then the signal’s entirely propagating in the dielectric, and obviously then the impedance depends entirely on the dielectric.

Edge-coupled microstrip has much lower dielectric sensitivity if you couple it strongly (small pair distance). And if you really want to be lazy, get a 2D field solver (like MMTL) and use coupled coplanar waveguide, clearing out the planes underneath the pairs until you get to the bottom layer. That solution has low dielectric and stackup sensitivity, because the signal’s tightly contained in a single layer.

Not sure I could get away with removing copper on layers below all that often, but it is an interesting tool to have in the toolbox I guess. :)

Typically I’ve been able to get away with edge coupling, and just pretending nothing exists underneath it. Things seem to work… but I must confess that I haven’t checked anything on a VNA.

I was going to write that I haven’t done anything as high speed as PCI-E before, but a quick googled suggests that it’s only 100Mhz … I don’t know why I assumed it was going to be higher than that.

“Not sure I could get away with removing copper on layers below all that often, but it is an interesting tool to have in the toolbox I guess. :)”

Look into it. These are the tricks that people use at very high speeds to manage excess capacitance due to pad sizes, for instance. See here, page 30. Even if you just do something as simple as void the planes below a pad with the size of the pad, you’ll bring parasitic capacitance down to the ~0.1 pF level.

It actually shows up at much lower frequencies than you’d expect, too! If you just take one of the edge-mount RF connectors and blindly use the layout they give you on, say, a multilayer board, even at ~100 MHz, you’re throwing away 10% of your signal or so. That’s because the dimensions they *give* you are intended for a *2 layer board*, and the capacitance of the pad with a ground plane right below it is *way* higher.

So you clear out the planes underneath the connector to effectively *make* a 2 layer board in that area.

“I was going to write that I haven’t done anything as high speed as PCI-E before, but a quick googled suggests that it’s only 100Mhz”

Nonono! That’s the reference clock. The actual signals themselves are in the GHz range.

Interesting stuff, thanks! Will definitely keep that in mind. I guess just clearing out at least one copper layer below is going to get you a core + a prepreg’s worth of distance to the next conductor on a 4 layer board.

Slapping my head a little on the data line speed of PCI-E. I mean, if you can get a whole bunch of peripherals much higher speed than USB on a PCI-E card, of course the data rate has to be much higher than USB.

This is very doable on a 4-layer stackup. On a standard (such as Elecrow or Seeed) FR4, .062″ (1.6mm) typical spacing to the inner ground plane is ~6mm. Using 6mil trace with 6mil spacing gets you 100 ohm +/- 10% differential impedance. Done! Just remember to use coupling capos between the power planes if you cross them.

“This is very doable on a 4-layer stackup. On a standard (such as Elecrow or Seeed) FR4, .062″ (1.6mm) typical spacing to the inner ground plane is ~6mm.”

This is just coupled microstrip, not edge-coupled CPWG. I’d also usually recommend tightening the conductor-to-conductor spacing to the minimum allowable (e.g. 4 mil) since it tightens the field to propagate as little in dielectric as possible.

“Done! Just remember to use coupling capos between the power planes if you cross them.”

Why in the world would you run a differential pair over a ground plane? You get proper impedance at ~mil distances. Decoupling caps might as well be miles away – the return current needs to hop to the top layer, across, and back down. I’ve seen this recommendation elsewhere, too, and I’ve simulated it, and it’s, uh, not great. You’re way better off just providing a nice return path on the power plane, and getting off of the layer adjacent to the power plane as soon as you can.

Just put a solid ground plane next to the differential pair if you *have* to run one next to a power plane. The power plane doesn’t have to be *all* power. Just make sure you provide return vias for the return current if the pair changes layers (and stitch near the endpoints, obviously)

I was reading your comment about Microstrip and was wondering how they achieved 100R with the layup and trace width/gap of 0.13/0.25mm. They would need a 0.2mm separation between layers to achieve anything close to that in FR4. And they didn’t void out the ground planes under those traces. Am I missing something?

Really like this, but what about Secure/Trusted boot?

For broad adoption in commercial applications some degree of trust is a must-have. Any indications on whether Broadcom will work with Pi-foundation to enable this?

The Pi was never designed for that. I’d never use one in a production setting.

The Pi wasn’t, but Pi compute module at least is touted for exactly this. From the Pi foundation site:

“Over half of the seven million Raspberry Pi units we sell each year go into industrial and commercial applications, from digital signage to thin clients to process automation. Many of these applications use the familiar single-board Raspberry Pi, but for users who want a more compact or custom form factor, or on-board eMMC storage, Compute Module products provide a simple way to move from a Raspberry Pi-based prototype to volume production.”

All the examples they give have trust/security factors. Seems reasonable that they’d figure out some way to make Broadcom security features available to OEMs.

And here I am wondering if I could build a custom dashcam or better up Cam (ala hikvision) out of this. Given I’m tired of being sold features and for a form factor… Jellybean a Poe, find a nice camera module…

dude! – https://store.gumstix.com/cm4-poe-smart-camera.html

well that was fast…

“According to the datasheet, across-pair lengths are significantly less critical, but between two lines in a differential pair, it pays to match lengths. KiCAD does differential pairs since CERN added it in 2015, and Saturn PCB toolkit comes highly recommended for calculating impedance-controlled trace widths, but it’s Windows only.”

Why recommend a canned solution solver? Those guys only solve the “known analytic solution” cases, and there are a bajillion of them. Qucs, for instance, comes with one, and a bajillion are present on the web. Or you could just, y’know, *look up* the solution if you wanted.

There are quite a few “arbitrary geometry” solvers out there at this point. ATLC (or MDTLC for a GUI) or MMTL, for instance. For a while Ansoft offered a free 2D field solver (Maxwell 2D) and I still have my copy of that.

The nice thing about a 2D solver is that you can figure out, for instance, what the effect of putting a shield with a via fence for crosstalk isolation at some distance will be. Obviously you can put it “far away” but sometimes it needs to closer just due to spacing. Can also figure out what the effects of clearing planes below will be.

I don’t understand the point of ‘compute module’ sort of boards like this, because it seems most people will need to buy an i/o expander. Anyone sophisticated enough to make their own board for this seems like they are only a few steps away from making the CPU board as well.

But the old one at least, I could imagine someone might get a backplane kind of board to pack a dozen of them in a relatively tight enclosure…it’d potentially be tighter than putting a dozen processors on a single board, because the CMs are at a right angle to the backplane. But this design makes that impossible, so I simply don’t get it.

Is anyone going to use this thing without also buying an I/O expander board? What’s the advantage compared to just releasing a variety of regular pis with different I/O exposed?

“Anyone sophisticated enough to make their own board for this seems like they are only a few steps away from making the CPU board as well.”

Layer count and assembly costs. Trying to stuff everything on the CM boards likely requires at *least* an 8-layer board, likely with fairly high quality, and then it’s also 2-layer assembly with tiny freaking components.

An I/O expansion board’s a joke. Easy to shove everything on one layer, and at most a 4-layer board. This is something you can get assembled dirt cheap, even at the prototyping level. *Especially* if assembly houses start adding that connector.

well don’t think so closed minded, I and others I know used the compute module to drive a lot of different hardware and this was quite a benefit that we could focus on our hardware and software without maintaining the whole linux and OS layer. Also the huge amount of working software is a major factor for small and medium companies.

We for example used more pins than on the normal PI, or a different usb hub.

To be honest, I think the CM4 & Arduino Pro series are looking to take on more industrial applications. It seems like a necessary step for RPi, to move into more professional circles – theres a lot of people making carriers or tools for carriers

The big advantage to this method of letting us at the SOC’s hidden skills is that it doesn’t cost the Pi foundation an enormous fortune supporting, and validating all these differently I/O equipped boards. But its also nice from the users point of view – the postage stamp of power is small and easy to integrate into a design of almost any shape and size. If you went and released a Pi with both camera lanes and display lanes somebody would be peeved that the HDMI is missing, or not on the same side as the USB etc etc..

They have done the hardest part of making a system that works – its an entire working computer already done for you. All the end user has to do is make the breakout board for the interfaces they actually need – and while the higher speed bus on this Pi vs the old ones will make that a little harder, its still comparatively trivial.

>The first group includes PCIe and USB, and within pair they need to be matched down to 0.15 mm, with 0.1 mm recommended for PCIe.

The datasheet said:

>2.4. USB 2.0 (Highspeed)

The USB 2.0 interface supports up to 480MBps signalling. The differential pair should be routed as a 90Ω differential pair.

The P N signals should ideally be matched to 0.15mm

USB 2.0 spec specifically ask for 100ps max skew. Remeber that it is only 480Mbps. We are not talking about 10Gbps.

https://electronics.stackexchange.com/questions/52851/usb-differential-pair-length#52861

>Added: On a real PCB, your signals travel slower than speed of light. For a stripline (inner layer) you divide the speed of light in vacuum by the square root of the relative dielectric constant (e_r). So about half speed. This means the 100ps is more like 15mm. For the outer layers, the speed is slightly higher (about 10%).

That’s like slipping 2 decimal places. 15mm (actually needed) vs 0.15mm is 2 orders of magnitude difference. :P

Hello, nobody has trouble to open Kicad files ? Tried to open it with latest release (5.1.7) on windows and mac but same error message : “KiCad was unable to open this fil, as it was created with a more recent version than the one running.

To open it, you’ll need to upgrade KiCad to a more recent version.

Date of KiCad version required (or newer): 08/29/2020”.

Yes, I do have the same problem, so it’s not just you…

you’ll want to use the nightly KiCad builds to open those files, then.

As far as I can see, this module doesn’t follow any standard SOM interface standard.

for example:

https://www.linaro.org/news/linaro-announces-launch-of-96boards-system-on-module-som-specification

or the older Qseven style

Why link an interface standard that doesn’t even map 1-n? Like the PI’s got more CSI/DSI lanes than is supported for example.

TBH his isn’t nearly as bad as yours

IEEE 1588 support in the PHY is nice, but I don’t see any datasheet for this part, or any part like it. Linux doesn’t have 1588 support for this PHY either.

I see SYNC_IN and SYNC_OUT pins which sound interesting, but there’s no info on them. Can they be used to accept a GPS PPS to synchronize the PHY’s clock?

I haven’t seen that particular connector style in a long time, and for good reason… The last time I saw it (circa 2001 or so?), it was the root cause for massive reliability problems in the laptop I saw it in.

What do you mean with connector style? Because the setup that theese seem to have, with connector elements on the sides/center, are used in all manners of cellphones, and industrial powertools.

If they are built like they should, they are basically impervious to vibration/shock and thermal fretting. I’ve tested derivates like this myself with excelent results.

The four screws ought to hold the CM down pretty well. It won’t be hanging on by the connectors alone.

That’s really amazing. This kind of template PCB sounds like the perfect help to get into laying out high speed traces and connecting up to high speed connectors.

It should be a very useful learning experience, with a known good reference. Excellent!

Anyone know anything about Gumstix??? Looks like you can build carriers for the CM4 here? (gumstix.com/special-offer)

I still can’t believe Gumstix still exist. They were the 2002 Raspberry Pi, except $200mhz ARMv5 for $400 a board with no carrier.

Good question! I’m also interested in this offer. But with their “normal” prices i’m not sure if it’s not cheaper to reduce the original Pi IO board design in KiCad and try my luck at JLCPCB.

Makemake wau e like me ka form factor ADD e luku nei i ka ʻoihana kamepiula liʻiliʻi.

Using a USB3 to SATA adapter on my Pi4B 8GB, and a Samsung 860 EVO 500GB SSD, I get 390-395 MB/sec write and similar read speeds… So why all the hoo haw over a PCIe NVMe drive doing the same, but requiring additional circuitry etc?

Actually, on a carrier board using the compute module it is less circuitry to connect the PCI Express directly to the NVMe module. On the single board computer they have a PCIe to USB3 controller so USB3 makes the most sense.

Does anyone know when it will actually be for sale?

Pimoroni – one of the official approved resellers – said “November”, but they weren’t any more specific than that.

I just ordered two from Canakit and they say it will ship on November 9th.

Thanks guys, much appreciated.

Yeah, I ordered mine at the same date. It was supposed to ship on Nov 30th. Just checked & the order says ‘pending’. Emailed for status, but they haven’t replied.

We get a new form factor every few years. When what we really want is equivalent to a cage of S-100 BUS slots or a stack of PC/104. And because of the shifting sands of form factor there is very little cross-vendor support, and we have bins full of legacy products that can’t plug into anything.

Exactly!

This makes me want to throw a simple pcb design with just gpio, hdmi, ethernet, sd card slot and single usb, coupled with 24 to 5v converter and see it works, probably fail miserably and try again until I’ll get it to work

https://geppetto.gumstix.com/#!/dashboard/

Hope this helps :)

>on the MXL7704

wouldnt that be “MXL7704-P4”? the custom programmed and unobtainable proprietary version?

Is this article copied from here (https://www.haveeru.com.mv/new-raspberry-pi-4-compute-module-so-long-so-dimm-hello-pcie/) or vice versa?

Wow! Thanks for that. We’ll have to send them a fistful of lawyers.

But yeah. I wrote it. You can see my trademark recycled moving-paper neutral background in the images.

Did he ever reply? Wrote a neutral “;P” comment to “his” article. Lets see if he activates it… XD

Does anyone know if this one has composite video out still? I couldn’t see it on the pdf description, but they didn’t make composite output that clear on previous boards either.

Yep. Looks like pin 111.

“Breaking with tradition is traumatic, and we know that some of you will be left with a closet-full of SO-DIMM sockets, but they did it for a good reason.”

“Packing PCIe alongside twin HDMI and other high-speed peripherals into the old SO-DIMM connector was just not possible”

Well, it sounds to be a good reason to replace with DDR4 SO-DIMM connector, but this mezzanine is a nightmare. And yes, DDR4 SO-DIMM is enough for HDMI and PCIe.

yeah, someone should tell NVidia that it wasn’t possible to use sodimm for HDMI and PCIe like they did on the jetson nano…

Sodimm it’s just a style, not a statement of capability. The Nvidia Jetson uses the MXM connectors which were designed from the ground up to provide the proper impedance parameters for high-speed graphics. Using them for PCI Express or other high-speed serial interfaces is quite common. I had hoped the raspberry pi foundation would use either the MXM connector or the 240-pin DDR3 sodimm, but alas it was not to be.

I’ve spent the last year designing a compute module (CM3+) based product with “upgradability” being one of the major selling points. I am within about a month of release. The form factor change is more than a little disappointing to me….

I feel your pain! I have two custom boards that I’ve done for people, but I did warn them previously that if they added USB 3 or PCIe to the next module there was no way the 200 pin sodimm would fly. I was hoping they would go with the 240-pin DDR3 sodimm which would certainly have the necessary bandwidth. But, nobody asked me!

There is commercial adapters https://store.gumstix.com/cm4-uprev.html

So I’ve started work on adapting my design to the CM4 and just realized they dropped the extra GPIO that the CM3 had! I NEEDED THOSE! GAAAAH! Not… exactly sure how I can make my product work anymore….

I didn’t notice it in the article until I started changing my schematic, but the new design has 200 pins just like the old one…. so it isn’t lack of pins that brought on the change.

“Found this gem of a pullup resistor on the SD card power switch.” But also not! PCBs are done by pick-and-place automated process, but that SMD resistor is soldered by hand. It means that is a workaround, someone mess the PCB schematic and forgot to add the resistor, so they was forced to post-work-by-hand all the messed up boards and add manually the resistor.

that “gem” will disappear in the next-revision of the board.

“Found this gem”.. pfffffh….

Getting ready to update my custom CM3 carrier to a CM4. Anyone know what mezzanine connector this is? I’ve looked through the datasheet and could not find any details on it. I thought I’d whip up an Eagle file, but not sure which part to add.

The article says that it’s Hirose DF40C-100DS-0.4V

Some say it might be this one: Hirose DF40C-100DS-0.4V

https://www.digikey.com/en/products/detail/hirose-electric-co-ltd/DF40C-100DS-0-4V-51/1969476

https://geppetto.gumstix.com/#!/dashboard/

There’s already a CM4-CM3 adapter available (for a price). But, you might also be interested in the online geppetto design app, which allows you to design/modify custom CMx carrier boards. They also offer assistance in manufacturing/marketing your products.

Hope this helps folks to get the CM4 ball rolling, if they ever start actually shipping the modules. I’ve been looking at a module(less) Gumstix CM4 NVMe carrier board for over a month, while wondering when/if the CM4 will arrive from Canakit.

I’d really like to get a Fritzing part for the 100 pin connector. Anyone know of a ready made part that can be downloaded? I have a 3D model and Solidworks but don’t know how to make Fritzing parts from that.

Nevermind, I’m 75% done with a custom part. We’ll see if it works and if Aisler can work with the resulting file. I know Fritzing is frowned upon by some but it’s all I know in this arena at the moment. I installed Eagle but haven’t been able to stumble my way through it yet.

Are there any developments with a slim CM4 base board where there is a 22x80mm M.2 slot on the PCB’s backside? Such a board could probably be as small as 85x65mm, with Ethernet, USB, HDMI, USBC power delivery.

And ideally a chassi. The https://tofu.oratek.com/ is the best fit today, in April they will release a 22x80mm M key M.2 adaptor to their current M.2 22x80mm B key M.2 slot. And there is a chassi available for 3D printing.

See discussion here https://www.raspberrypi.org/forums/viewtopic.php?f=98&t=293256&sid=61e936e2d8dc573a04192277e987b8cd