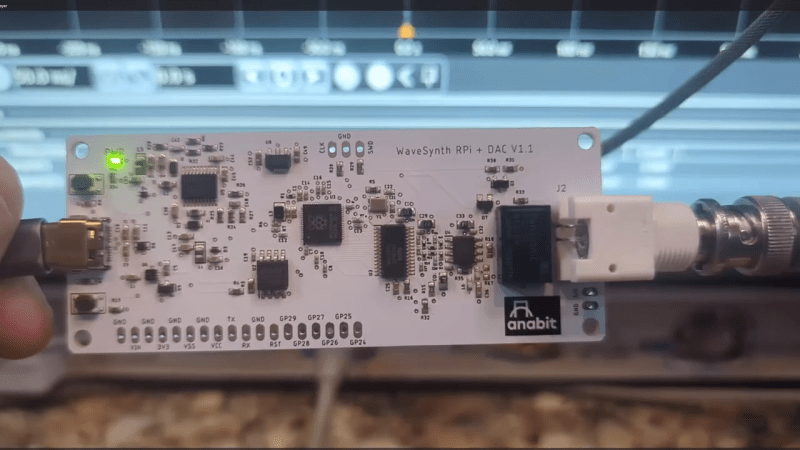

Normally, if you want to blast out samples to a DAC in a hurry, you’d rely on an FPGA, what with their penchant for doing things very quicky and in parallel. However, [Anabit] figured out a way to do the same thing with a microcontroller, thanks to the magic of the Raspberry Pi Pico 2.

The design in question is referred to as the PiWave 150 MS/s Bipolar DAC, and as the name suggests, it’s capable of delivering a full 150 million samples per second with 10, 12, or 14 bits of resolution. Achieving that with a microcontroller would normally be pretty difficult. In regular linear operation, it’s hard to clock bits out to GPIO pins at that sort of speed. However, the Raspberry Pi Pico 2 serves as a special case in this regard, thanks to its Programmable I/O (PIO) subsystem. It’s a state machine, able to be programmed to handle certain tasks entirely independently from the microcontroller’s main core itself, and can do simple parallel tasks very quickly. Since it can grab data from RAM and truck it out to a bank of GPIO pins in a single clock cycle, it’s perfect for trucking out data to a DAC in parallel at great speed. The Pi Pico 2’s clock rate tops out at 150 MHz, which delivers the impressive 150 MS/s sample rate.

The explainer video is a great primer on how this commodity microcontroller is set up to perform this feat in detail. If you’re trying for accuracy over speed, we’ve explored solutions for that as well. Video after the break.

Nice advert.

And thus, the Beaglebone Black was rerereborn.

“you’d rely on an FPGA” : you mean… a DSP?

What the use case for that? If it had been an ADC I’d say signal acquisition, but with a DAC? Is it for generating sound?

Could generate radio signals (unfortunately it’s filtered, restricting to below 27MHz mostly)

AWG

I wouldn’t mind something like this as a Function generator for analog designs. Like testing (noise) filters and EMI behaviour. A fast one running at 25Mhz can easilly set you back a couple hundreds.

There is an el-cheapo chinese signal generator that can generate 14bit at circa 250Mhz sampling producing 60Mhz sine wave easily. I got one for around 60 UK pounds many years ago. It was based on an STM32F103 for the user interface and an FPGA doing the fast bit stuffing into a fast DAC. This design has been copied by a variety of chinese manufacturers. It even could do arb generation. Think it wa FYxxxx or similar.

I buy digilent Discovery kits on Facebook for less than $100 from college kids who were required to buy them for a course. The free software that is downloaded to run them is worth $100,000 in Tektronix $$. I run two and that nets me four channels of function generators, scopes, power supplies etc. I am soon to be selling nearly all of my dedicated test equipment to use them exclusively. After that I will buy two more and have eight channels. If working with line voltages just be sure to use a USB isolator feeding a USB hub. I learned the hard way that the digilent discoveries aren’t isolated from ground.

Nice, if I ever need 1.7 milliseconds of 150 million samples per second. I know where to come

You can use it as an arbitrary wyvern germinator, aka an AWG.

Not to be confused with an ACWG (arbitrary and capricious wyvern germinator), a different beast entirely.

You can do the same thing with any modern microcontroller (like an STM32 or LPC) using DMA transfers.

For 150MSps out you can’t just DMA into GPIO. Some STM32 peripherals such as LTDC could be used, but I think that also tops out at 100MHz.

Meanwhile RP2xxx can easily be overclocked to 250MHz and with luck the signal waveforms are not too bad either.

This could make a nice arbitrary waveform signal generator.

cool it with liquid helium for 150 MHz clock?

150mhz is RP2350 stock clock

No, pico 2 doesnt top at 150, it starts at 150 MHz. Just because Anabit says “The RP2350’s maximum clock rate is 150 MHz hence why the PiWave is a 150 MS/s DAC” doesnt make it true, which they later admit themselves :)

1 For example RP2350 based logicanalyzer goes all the way to 400MHz overclock https://github.com/gusmanb/logicanalyzer/blob/39a7a0b43fa2de03927cc17ce397b2fc4fbe314b/Firmware/LogicAnalyzer_V2/LogicAnalyzer_Board_Settings.h#L39

2 RP2350 HSTX allows IO to work in DDR mode, effectively doubling output speed

3 Considering preceding “RP2350 allows you to output its clock from one of its GPIO pins” in Anabit sales pitch “maximum clock” sentence was most likely about PLL clk_gpout output frequency and not microcontroller clock rate itself.

4 Except they dont even need clk_gpout and could have clocked DAC with normal IO pin as IO is already synced to sys_clk

5 Later on they admit real limitation is BB DAC900 “The RP2350 can be over clocked, but maximum sample rate of DAC IC is 165 MS/s”

6 Anabit is still overclocking because official RP2350 datasheet states “You can also output up to 4 generated clocks to GPIOs at up to 50MHz.” meaning anything over 50MHz out of clk_gpout is officially out of spec :). I suspect official RP2350 documentation is outdated or mistaken because 50MHz is coincidentally also official maximum clock rate of accepted crystals/external clock sources driving XIN, but this doesnt take into account whole PLL equation FOUTPOSTDIV = (FREF / REFDIV) × FBDIV / (POSTDIV1 × POSTDIV2)? Without defining additional dividers clk_gpout is in fact outputting full FOUTPOSTDIV and there are projects taking full advantage of this fact (pico-fractional-pll).

TLDR a lot of confusion because it is in fact confusing.

Good morning, Can I use the same in Telemetry station for Stripchart recording?