It’s one thing to create your own relay-based computer; that’s already impressive enough, but what really makes [DiPDoT]’s design special– at least after this latest video— is swapping the SRAM he had been using for historically-plausible capacitor-based memory.

A relay-based computer is really a 1940s type of design. There are various memory types that would have been available in those days, but suitable CRTs for Williams Tues are hard to come by these days, mercury delay lines have the obvious toxicity issue, and core rope memory requires granny-level threading skills. That leaves mechanical or electromechanical memory like [Konrad Zuse] used in the 30s, or capacitors. he chose to make his memory with capacitors.

It’s pretty obvious when you think about it that you can use a capacitor as memory: charged/discharged lets each capacitor store one bit. Charge is 1, discharged is 0. Of course to read the capacitor it must be discharged (if charged) but most early memory has that same read-means-erase pattern. More annoying is that you can’t overwrite a 1 with a 0– a separate ‘clear’ circuit is needed to empty the capacitor. Since his relay computer was using SRAM, it wasn’t set up to do this clear operation.

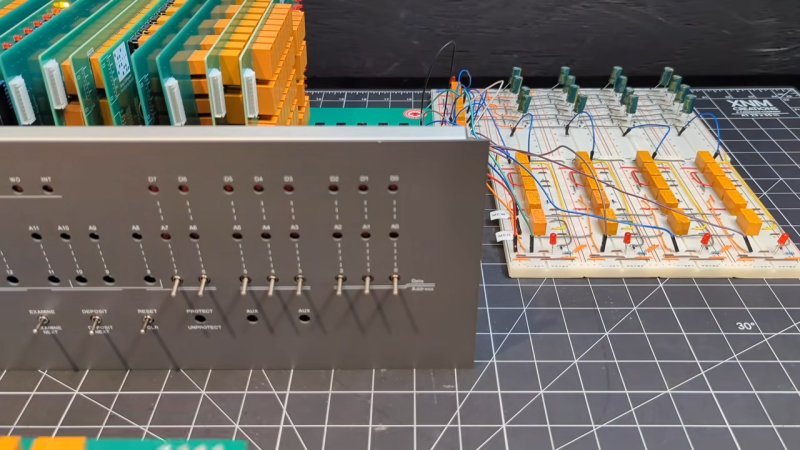

He demonstrates an auto-clearing memory circuit on breadboard, using 3 relays and a capacitor, so the existing relay computer architecture doesn’t need to change. Addressing is a bit of a cheat, in terms of 1940s tech, as he’s using modern diodes– though of course, tube diodes or point-contact diodes could conceivably pressed into service if one was playing purist. He’s also using LEDs to avoid the voltage draw and power requirements of incandescent indicator lamps. Call it a hack.

He demonstrates his circuit on breadboard– first with a 4-bit word, and then scaled up to 16-bit, before going all way to a massive 8-bytes hooked into the backplane of his Altair-esque relay computer. If you watch nothing else, jump fifteen minutes in to have the rare pleasure of watching a program being input via front panel with a complete explanation. If you have a few extra seconds, stay for the satisfyingly clicky run of the loop. The bonus 8-byte program [DiPDoT] runs at the end of the video is pure AMSR, too.

Yeah, it’s not going to solve the rampocalypse, any more than the initial build of this computer helped with GPU prices. That’s not the point. The point is clack clack clack clack clack, and if that doesn’t appeal, we don’t know what to tell you.

So, it’s basically DRAM with relays? Interesting what-if. The other option would be to create relay base SRAM with latching relays.

the dram uses capacitors so small that it cant hold charge very long and need constant refresh, these things seem to be able to hold charge for days. more of a refresh when idle situation. you cant make it very fast or very dense though. perfect for a relay computer though.

Very costly with relays, a DRAM thingy works very well at the clock frequencies a relay computer uses (usually sub-khz), and then a matrix organization would reduce the number of relays.

Might be worth it for registers though?

“most early memory has that same read-means-erase pattern”

this is also true for the GB of RAM that fit our modern computers: all DRAM

Konrad’s name was Zuse …

One of my heroes, together with Alan Turing and Seymour Cray.

Typo corrected, your imperial majesty.

Maybe there is a language barrier here, but this comment comes off as very snarky, particularly on a request to fix someone’s name that you spelled wrong. Please keep in mind the below comment policy: “Please be kind and respectful to help make the comments section excellent”.

Kaiser means emperor.

Gotcha, thank you.

Kaiser (/ˈkaɪzər/ KY-zər; German pronunciation: [ˈkaɪzɐ]) is the title historically used by German and Austrian emperors.

The Atanasoff–Berry computer built at Iowa State (1939-1942) used 3200 capacitors for memory.

Excellent recollection. The IBM 650 computer also used capacitor memory for its registers. For this machine, each bit was implemented with a capacitor and two vacuum tube diodes.

When I attended ISU many years ago they had one of the surviving beeswax-filled capacitor drums on display in the engineering building. Decades later I got a chance to see the replica they built when they took it on tour.

I’ve made capacitor relay memory before for a relay CPU project, and it can be made so it doesn’t need a refresh after read (the capacitor charge is only used to turn on an driver relay, once that occurs the relay charges the capacitor back up).

One problem that is difficult to authentically resolve is the relay back EMF damaging the polarised electrolytic capacitors, so they quickly fail. Non-polarised electrolytic are expensive, and other types are too small to store enough charge. You can use diodes to stop the EMF, but then it isn’t period-authentic in any way, and you might as well make transistor-based SRAM.

Another memory type being used by The National Museum Of Computing (TNMOC) in the UK is a nickel delay line. This was chosen for the EDSAC computer reconstruction to replace the original mercury delay line as less toxic.

I wanted to try a glass delay line, used in early PAL colour TV receivers, but they became unobtainable before I conceived of the idea. I still wonder if it could have been made to work.

Many SMD caps on a flexible PCB wrapped around a rotating drum for much more, but longer access time memory?

“The first regenerative capacitor memory built was the rotating capacitor drum memory of the Atanasoff–Berry Computer (1942). Each of its two drums stored thirty 50-bit binary numbers (1500 bits each), rotated at 60 rpm and was regenerated every rotation (1 Hz refresh rate).”

The BBC used to have a 525 line/60Hz to 625 line/50Hz standards converter that used multiple capacitors as the analogue line memory. I can’t remember the exact number but it was several hundred.

Aaahh, a computer for my .. ears. It sounds a bit Kraftwerklike. Bring two more, one with lower speed for the bass, one overclocked for the high notes and the lights will fill the dance floor.

Kewl. Simply kewl!

Years and years back I was looking at the local surplus sales where they were getting rid of the step relays from gutted local PBX thinking “that would be one interesting memory cell to design and build for nada”.

Obviously, I had other priorities at the time (family, etc), but the point remains, with some clever redesigning/reengineering step relays can be made to switch 16 positions per, and since they are relays, can double as the line switches, ie, connecting blocks of other step relays in different ways/combinations.

Just thinking out loud; for some amateur projects I’ve done 4-bit logic was plenty enough, and bistable low-power relays were what I’ve used for simple static RAM of sorts. I still think that I am going in the wrong direction with “everything HAS to be binary logic”, since relays in themselves are already mid-way between binary and analog, and things like op-amps would complement binary with some analog computing, perhaps bypassing the need to have it THAT advanced.

Something like that.

How about an electronic calculator that uses this technology as its register storage? https://oldcalculatormuseum.com/toshbc1411.html. This was state-of-the-art for an electronic calculator in 1966!