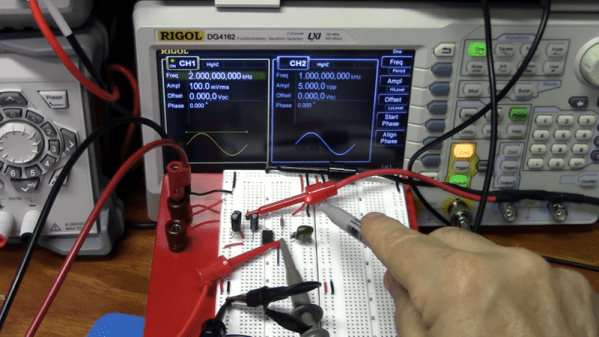

When Hackaday runs a contest, we see all manner of clever projects. But inevitably there are some we don’t see, because their builders didn’t manage to get them finished in time. [Park Frazer]’s phase-locked loop is one of them. The circuit is an all-discrete PLL that derives a 440 Hz output from a 1 Hz input, and it arrived just too late for our 1 Hz contest.

If you aren’t familiar with a phase-locked loop, in this context you can think of them as a programmable frequency multiplier. A voltage-controlled oscillator is locked to an input frequency by comparing the two with a phase detector. Multiplication can be achieved by putting a frequency divider between the oscillator and the phase detector. It’s at the same time a complex and easy to understand circuit. In this case, when broken down into a set of multivibrators, it makes sense. The charge pump phase detector is a little different from the XOR gate we were expecting, but as he explains, it’s better.

If PLLs are a mystery, have a look at this video from a [Jeri Ellsworth] and [Bil Herd].