If you are in the market for an inexpensive USB logic analyser you have a several choices, but few of them deliver much in the way of performance. There are kits from China for a few dollars using microcontrollers at their heart, but they fail to deliver significant sample rates. If you require more, you will have to pay for it.

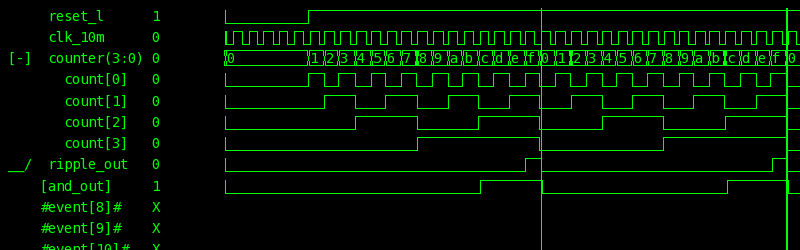

It is therefore rather interesting to see [kevinhub88]’s SUMP2 project, an open source logic analyser with a claimed 96 MSPS sample rate using an off-the-shelf Lattice iCEstick FPGA evaluation board that only costs about $20. It talks to a host computer via USB using the established SUMP protocol, so its software front-end comes from the sump.org logic analyser project. Edit: Since this post was published [Kevin] has contacted us to inform us that the project’s capabilities have now moved beyond SUMP’s capabilities and in fact it now uses his own software.

This project has the promise to add a very useful piece of test equipment to the armoury of the engineer on a budget, and to aid the cost-conscious reader he’s provided extensive documentation and installation instructions, as well as the code for the FPGA. Thanks to one of the more awesome hacks of 2015, there is an entirely open toolchain for this Lattice part, and our own [Al Williams] has written up a multi-part getting-started guide if you want to get your feet wet. You probably want one of these anyway, and now it’s a logic analyzer to boot.

We’ve covered quite a few inexpensive home-produced digital instruments here over the years, including this logic analyser with a slightly higher price tag, this inexpensive VNA, and this oscilloscope board. Maybe one day the bench of our dreams will all come on one open-source PCB for $100, who knows!

judging by my clumsiness and past broken boards, i would like more products to be shipped with micro/mini USB instead of an A but that being said to lattice i am picking up one of those boards and i’ll sure as hell be giving it a shot

my logic analyzer is getting a bit dated for the high speed logic i’m working with these days

I completely agree. Any old USB 2.0 A extender cable works great with this board and removes to opportunity of doing tremendous torque damage.

I do use one now (i have one on every port actually on my desktop) but i have found on one board (it was either an RTL-SDR dongle or a bluetooth sniffer i cant remember) the A port solder joint got loose and lifted a pad (causing me to get past my shaky hands for a repair)

Even mini and micro are still pretty delicate. Unless a device needs to act as both host and device and absolutely cannot have two separate connectors I would skip those two and go right to USB-B.

Could this run on a PI with reasonable performance? There is your 100$ 92mhz logic analyzer with display, mini keyboard and mouse/trackpad.

Yes it could run on a Pi with reasonable performance, especially a Pi3. The original Python was actually developed on a Linux workstation ( Python 2.6 ) but ported to Python 3.5 to run on Windows for certain reasons. The problem I have found with most Linux distributions is that they come with older pre Python 3.x. Today, the sump2.py application only works on Windows, but the Window specific things are very few ( mostly STDIN console stuff ).

Cool, sounds good! I ordered a board and I will definitely test this. Actually one of the tools I have been waiting for! I’ll take a look at sump2.py sources but I hope someone with more Python experience will port it over to linux… This project certainly deserves a handheld packaging with a battery…

I might be able to explore that. One of my other projects is embedding full screen PyGame apps ( such as sump2.py ) on a Raspbian-Lite image modified for driving a 3.5″ TFT. Full write-up is here.

https://blackmesalabs.wordpress.com/2016/10/09/easy-path-to-running-embedded-python-on-a-raspberrypi/

My concern with joining this with the SUMP2 project is that the screen resolution is very limited compared to a 24″ 1080p monitor ( 3.5″ TFT is only 480×320 ) and sump2.py definitely requires a mouse. The included stylus just wouldn’t work.

Imo using those SPI-driven screens for an RPi is an error in most cases. The refrest rate sucks and you have no hardware acceleration. You get something proper with an HDMI-connection for ~20€, e.g. http://www.ebay.de/itm/141939860738. The touchscreen is still connected via SPI, but works almost oob: http://lektiondestages.blogspot.de/2016/06/properly-setting-up-5-hdmi-touchscreen.html

What part of “windows only” sounds good?? Every hacker running a non-free OS should be ashamed of him/herself.

LOL, you can totally get windows for free. My copy of windows 10 enterprise was free through their insider program.

I spend 90% of my time developing in Linux, so your words don’t offend me. 75% of the 6,000 lines of Python in sump2.py was developed on a Centos distribution running Python 2.7 – this was in 2013. Today, 2016 – I had a specific use case where this project HAD to work on Windows 10 and Windows 7 running modern Python 3.x, so that is what is what developed and tested on. The software is 100% Python which is platform portable unlike .NET but it DOES require modern Python 3.x, PyGame and PySerial. All of my Linux machines including new Jessie-Lite image only come with Python 2.x. – which is a problem, so at this time, I didn’t even bother to try and run it on my Linux machines. There are like 10 lines of Python out of 6,000 in sump2.py that are specific to Windows 7/10 that were needed to get a functioning command line interface working. That is it. Find me a Raspbian Jessie-Lite that comes pre-installed with Python 3.x insead of Python 2.x and then there is a viable platform. Upgrading Python versions on Linux distros is a royal pain, I’d much rather wait for the distros to catch up with Guido and the rest of the Python community.

You might want to look into http://www.icoboard.org This board is more capable, has 1 MBit memory on board, fits nicely on a raspberryPi, the FPGA toolchain runs on the RaspberryPi, you can add fast AD converters PMOD, has massive IO, and I even would send you one for free.

Icoboard looks very interesting. The larger FPGA would mean that 32 bits instead of just 16 bits could be sampled and also the RAM length would be much deeper. I must say I’m confused by these 3 replies of “I would send you one for free” from Eduardo, Humenberger and Linda. Are any or all of you associated with the icoboard.org group itself? If so, please contact me via email at the bottom of my “Welcome” page.

At least “Linda” seems very much like a bot to me

Does the Icestick have any SRAM? or is these some block ram in the FPGA. It seems too small a FPGA to have BRAM. I am always looking for cheap FPGA dev boards with SRAM (not SDRAM). The ‘1k’ what is that 1k macro’s or 1k regs/or logic units?

1K logic cells and 16 4Kb Block RAMs. The Logic Cells are a bit misleading. I have found that a lot of CLBs get consumed for route throughs. For example, technically the SUMP2 requires only 700 Flops and 700 LUTs, but the design is 100% full of 1197/1280 LCs. My next port of SUMP2 is the icoBoard. It is the larger 4K Lattice FPGA and they do have a external SRAM version.

Ok, 8kB BRAM is much more than I expected for such a small FPGA. That would make it very useful but still not enough for more RAM intensive processing. The 16 blocks may make it good for a tile based video output.

Oh and SI goes – p, n, u, m .. k, M, G, P – the ‘k’ is the odd one out as it’s lower case.

I always mess up the ‘k’. The ‘b’ I typed small as it is bits, not bytes. SUMP2 uses 48×1024, or 48kb of the total 64kb. Check out Spartan3 and Spartan6 for low cost FPGAs with gobs of onchip BRAM.

Look it icoboard.org I think it is a good fit with all its IO, memory, its a RasPi hat. You can add AD converter. And I would send you one for free.

I am so glad I found this comment it was very helpful to me! You might want to check out http://www.icoboard.org. I think is very good fit with much IO mmemory and RasberryPi cap. You can add ADC convert. And I would send you one for free!

schild, cap, balaclava. I’m getting confused with all these stretcher modules.

I’m not sure which distro(s) you run but most I have used come with both Python2.x and Python3.x. One or the other gets symlinked to /usr/bin/python. Changing that symlink from 2 to 3 may or may not break the distro’s package manager, config or startup scripts (since many of these use Python).

The actual executables will be python2.x and python3.x (where x of course is actually some digit) and symlinks will also exist that are simply python2 and python3. I’m guessing you probably have something like ‘#!/bin/python’ at the begining of your scripts. I would just replace that with ‘#!/bin/python3’ and it will probably work just fine on most distros.

If the distro’s package manager and other tools all use Python2 then it may actually be that Python3 is not automatically installed. apt-get install / yum install / emerge / etc… python3 aught to take care of it without having to remove Python 2 or break anything.

Thanx for the tip. I will look into this. I do a lot of “embedded Linux” projects with the Raspberry Pi, so I would like to get this running on a Jessie-Lite image full screen.

@kevinhub88, seems like Python 3 for Raspbian Jessie Lite is as close as “apt-get install python3”:

https://packages.debian.org/jessie/armhf/python3/download

What am I missing?

Great project, BTW!

Thank You! Yes, my next step is to go down the path of getting sump2.py to work with my Raspbian Jessie-Lite. I will most likely target both the iCEstick and the icoBoard. I am excited about the icoBoard as I will be able to use the Mesa Bus Protocol over SPI instead of UART ( about 20x faster ). Stay tuned to Black Mesa Labs.

Cheap is good. Open toolchain is even better. But, be aware it does not have any external memory. So the internal 64Kbit EBR is the only storage for a triggered snapshot. That’s only 2/3 of a millisecond at 96 MS/s @ 1 bit. It’s host interface is also UART instead of a traditional FX2 type interface. So I suspect you can only capture snapshots to EBR and not stream realtime at any usable bit-rate. OLS, DSLogic, and other alternative might be worth the additional cost.

The SUMP2 design does real-time compression of hardware transitions prior to storing to the limited on-chip SRAM. This means it is possible to store milliseconds of slow transitioning data ( for example, an I^2 link ) even though the hardware is sampling and storing with 96 MSPS timing resolution. You can’t sample a 40 MHz clock for very long, but for many applications RLE is very useful resulting in 10x – 1000x compression ratios.

Is it using UART mode? As the FTDI chip is the FT2232H it should be able to use one of the various faster modes that the FTDI chip supports, depending on what pins are connected

It uses UART mode for compatibility. It is easy to get Python to talk to a COM port at 921,600 baud, much more difficult to get modern 3.x Python to talk to FTD2XX.DLL. That said, the serial interface isn’t that bad of a bottleneck as it is used for downloading RLE compressed data. The data is all decompressed in software.

Should be possible to run it at 12MBaud – the actual rate can be hidden from the OS if necessary by tweaking driver settings to alias from a lower rate.

I was thinking that required FT_PROG, which is something I wanted to avoid as it gets overly complicated. The download is actually pretty quick as the RLE RAM is only 1Kx64.

Ah hah! RLE is… friggin’ obvious now that you mention it. What better case could there possibly be for it? Gonna keep that in mind.

Nice work, here.

Top project but there is one very prominent limitation and that is it’s only good for 3 Volt logic.

Still, in any case, if you want to try your hand at VHDL or Verilog then this is a nice simple project to get you on your way cheaply. Installing this design environment must be a pleasure compared to the Xilinx or Altera design environments.

I use this logic Analyzer ($50USD) –

http://dangerousprototypes.com/docs/Open_Bench_Logic_Sniffer

http://dangerousprototypes.com/docs/images/4/46/Ols-cover.jpg

It’s open source and open hardware.

I don’t often us it anymore. I seem to debug in software most of the time now but an analyzer is good for the old 5 Volt stuff.

But since someone has paved the path for me I might go and buy one of these to try Lattice. I currently only use Xilinx and Altera.

Thanks [kevinhub88]

I mentioned in my FAQ if there is enough interest in 5V ( old Arduino Unos? ) I am willing to design a daughterboard PCB with a LVC244 5V tolerant input buffer. Interested parties could buy the bare fabs straight from OSH-Park for like $5 and assemble them themselves. The nice thing about the 3V inputs straight to the FPGA is that they are fast enough to sample a 40 MHz signal without any external prop delays from a level translator. The thing with the level translator is that I suspect the people that would want them might not want to solder SMT ICs and little 0603 Rs and Cs. I could be wrong, just a hunch.

There’s definitely a drive. Automotive stuff exclusively uses 5v, and any tools made that can use 5v is a massive win for what I like tinkering with.

Kaluce – Yes – okay, I was looking for some feedback on this this and you gave me some. Thank you. I can design a 2-layer OSH-Park plugin shield board for 5V tolerance this weekend. Would you be willing to give me some input on your soldering capabilities? My issue is that I design PCBs with really small components and hand solder them under a microscope – which I realize not everyone is capable/willing to do. I have an email at the bottom of my “Welcome” page if you would like to contact me directly.

5V input shield is now available for purchase from OSH-Park. Please see site update.

I use this one too, and love it… it has been the most useful $50 spent for my electronics workbench (with a 30 year old o-scope for $50 being the next one).

The Open Logic Sniffer Java software https://www.lxtreme.nl/ols/ is an excellent alternative to the standard software, and works on Mac and Linux very well (never tried on Windows but assume it is fine there too).

Yes! This is how I got started on the SUMP1-RLE project. I purchased the SUMP compatible hardware from Sparkfun and used the excellent Open Logic Sniffer Java software with it. I then developed my own hardware which did RLE compression and decompression in hardware ( to work with the existing software ). I ended up adding a bunch of new capabilities that required I write my own software and stop using the excellent Java software.

$40 shipping on a $20 development board – well that killed it for me!

From where to where? I think Mouser only charged me like $8 from Texas to Washington state. This is what Arrow quotes: $23.31+$2.60 tax and $4.05 shipping

From the lattice website (shows “powered by mouser”) to Australia. I also looked in ebay and I can get one there for around $100 lol.

The Australia Element14 site quotes $43.40, which I am assuming is in Australian dollars, or about $33 in US. Maybe they have reasonable shipping. That price isn’t highway robbery anyways.

http://au.element14.com/lattice-semiconductor/ice40hx1k-stick-evn/ice40-hx1k-icestick-eval-kit/dp/2355207?ost=iCEstick&selectedCategoryId=&categoryNameResp=All%2BCategories&searchView=table&iscrfnonsku=false

I did the same double-take as RÖB.

Yeah, that’s in $AU and you can get free shipping from e14 for orders over $45.

I’m sure we can find $1.60 of sundries to get us over the line, thanks for the link.

You might want to get a http://www.icoboard.org . It is much more capable, costs 90 Euro and I would charge for shipping to australia only 20 Euro .

Looks like the board is also available from other suppliers (including Mouser (PN 842-ICE40HX1KSTICKEV) and Digikey (PN 220-2656-ND)) for a significantly lower shipping cost.

I saw they are $25.24 at Digi-Key. A little more expensive, but if you already have an order with them, then the extra few dollars balances out with your shipping costs.

And $21.86 + $44.65 shipping to Europe. :( ????

Everyone, my 3 links Lattice,Digikey and Mouser are all for U.S. Distribution ( as that is all that I know – sorry ). Please look around for your region. I did a quick search in China and noticed some reasonable prices – example $36

https://www.aliexpress.com/item/1-pcs-x-ICE40HX1K-STICK-EVN-Programmable-Logic-IC-Development-Tools-iCE40-HX1K-iCEstick-Eval-Board/32436885113.html?spm=2114.01010208.3.2.tI4bHP&ws_ab_test=searchweb0_0,searchweb201602_3,searchweb201603_3&btsid=346581df-55b5-423d-9499-901f20f764e5

Search for Lattice ICE40HX1K-STICK-EVN iCEstick

this looked great until I saw that used .net in the software..I try and keep it off my main PC…

This new version ( SUMP2 ) does not use .NET. It only uses Python. I abandoned my orginal SUMP1 .NET software from 2014 as it was too slow. Python is fast to develop in and fast in runtime operation.

my apology, I didn’t see that! well done then!

Genuine question: why not using sigrok as software?

It would benefit from the sigrok developments, for instance, new protocol decoders every now and then.

+1 thought the same thing. Plus theres an Android client for it already which would be awesome

I spoke with one of the core developers of Sigrok. The problem is that the internal SW structure of Sigrok does not fit well with FPGA based logic analysers. They said they want to restructure Sigrok so that they can do a logtic analyser with icoBoard. They even purchased an icoBoard. That was Dec 2015. I did not hear back from them since.

Interesting, if you look at their (long) list of supported-devices, the majority are FPGA-based.

Hmm, do you have some details about this? We discussed this a bit on #sigrok and no-one remembered such a conversation, and I found nothing in IRC logs either. Icestick/icoboard based analyzers have been planned but I guess no-one has been interested enough to actually do it.

I would be very open to working with the Sigrok community. sump2.py has no serial decoding capabilities, it is just a raw digital capture device. A definite complication is that the SUMP2 hardware stores RLE compressed data and the SUMP2 software handles all the decompression and proper alignment. Where it gets really complicated is when DWORDs of data are captured in parallel with the events. In the full configuration, the SUMP2 hardware captures 32 events to RLE RAM and 16 DWORDs ( 512 bits ) to non-RLE RAM. The software then has to properly align these databases. Definitely on the surface “Just use Sigrok” makes a lot of sense, it is under the hood where things get complicated.

I know that it is more difficult than saying “use sigrok” :)

However, I would have thought that implementing those extra features/capabilities (e.g. decompression, alignment) to sigrok would be easier than writing a software analyser software from scratch. Anyway, I have literally no idea how sigrok is done, so in reality I don’t know.

I know very little about Sigrok, but I suspect it is written in Java or C++. sump2.py is actually forked from chip_wave.py, a VCD waveform viewer I wrote 3 years ago ( similar to GTKwave ). Python is the only language I would consider writing a tool like this in, as it deals with lists and lists of lists, etc. I’ve written software in Assembly, BASIC, REXX, C, C++, C#, Powershell, Ada, Perl, Python. Of these, Python is the only one I would consider using as the foundation. It really is that much better.

I know this is just 24MSPS, but it’s compatible with some top-notch logic analyzer software. And it’s a mere 6.5 USD, with worldwide free shipping. If you don’t care about it being a knockoff and your signal is slower than 10MHz, you can’t get better than that.

ebay.com/itm/131752135890

Please don’t. This is a shameless knockoff of the Saleae Logic-8 hardware which requires pirated software to operate. Saleae.com is a small California company started by two brothers. Nice guys, I know one of them. They developed some excellent software and have made a profitable small company from it which should be every engineers dream. Please spend the $109 and purchase the Logic-4 from saleae.com. Their serial decoding software is fantastic and well worth the money. I use their $599 Logic Pro 16 USB 3.0 streaming analyzer almost daily and it is a fantastic product for deep capturing to Windows DRAM at up to 500 MSPS. The Logic Pro 16 is extremely capable and very easy to setup and use. I can’t say enough good things about the Saleae company, hardware and software.

While I don’t really like that he posted a direct link to a particular product/auction, I would like to comment on your claim that those logic analyzers hurt Saleae. The original Saleae Logic is really nothing more than a Cypress FX2 used in its most basic way. Saleae only wrote neat software to go along with it. Buying the hardware (heck, even an FX2 eval board will do) and using it with Sigrok is 100% legal and doesn’t hurt Saleae as they don’t even sell the original Logic anymore.

I completely agree so long as the FX2 boards are used with Sigrok software. I take issue with these $5 FX2 boards that have “Saleae Logic Analyzer” stickers on them. People who want to use the excellent Saleae software should be paying to use it. $109 is a tremendous value.

In case you have a BeagleBone Black lying around, its PRU’s can easily handle 100Msps sampling 14 channels with buffer size limited only by the onboard memory (hundreds of megabytes). Lack of hardware triggering is an obvious downside, also logic level shifting requires additional hardware. Check out the BeagleLogic project.