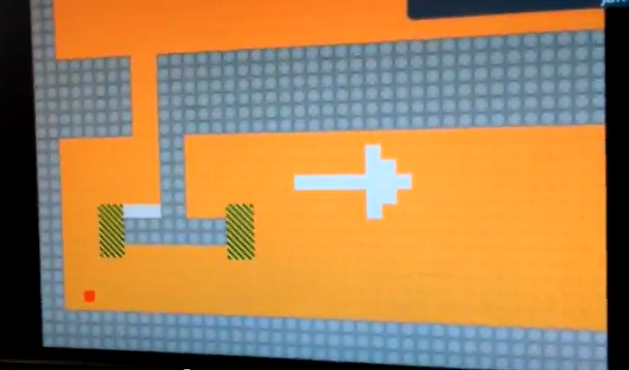

We usually look at these FPGA University projects and think how much fun it must have been to get credit for the work. But in this case we can’t image the grind it must have been to implement the game mechanics of Meat Boy in an FPGA. See how well it came out in the clip after the break.

Remember that with an FPGA you’re basically building hardware devices by using code. The Reddit discussion of the project sheds some light on where to start (and even shares the source code). The Altera DE2 is pushing the game to a monitor using SXGA at 60Hz. The map is laid out as a collection of 32×32 tiles, each represented by 2 bits in memory. [SkipToThe3nd] does go into detail about how the physics work but we can’t even begin to paraphrase that part of the discussion.

The game being cloned here is Meat Boy, the Flash game predecessor to Super Meat Boy. If you’ve never heard of the title we’d suggest watching Indie Game: The Movie, a documentary which follows several independent game developers as they try to get their titles to market.

Nicely done! I know the pain of getting these games to work properly, for a class i had to write a graphics card for the FPGA and a game for ARM. After 20 weeks ( 14 hours a week) with 4 other students the games would run poorly.

Please can someone explain to me why so many projects are done in VHDL. Verilog is far superior IMHumbleO, subjectively, a view which seems to be shared by anyone I’ve ever met. And objectively http://www.ee.ed.ac.uk/~gerard/Teach/Verilog/manual/Example/lrgeEx2/cooley.html whenever I see them tried side by side.

Who are these b******s(excuse the French) that insist on everyone using these crappy languages. I’m looking at you every college Java course. (let’s not even get started on c++)

I don’t know anything about Verilog vs VHDL, other than I’ve also heard that Verilog is much easier, but Java is a fine language to teach object-oriented programming concepts, it’s actually in wide use because of Android, and it’s C-like enough to allow an easy transition to languages like C#.

I personally have never been a fan of Verilog, mostly because of the lack of strict declaration – having wasted many, many hours debugging code only to find out my error was a misspelled wire name . . . well, I came to appreciate the fact that VHDL had strict checking. Other than that, having learned VHDL first, I disliked the fact that wires and registers were not declared differently in Verilog; from the hardware design perspective, a wire and register are completely different, and the difference between the two shouldn’t be found only through static analysis.

But they are both pretty heinous languages, there are (at least) as many faults with VHDL. But to answer your question, yes, there are reasons to choose VHDL over Verilog, and, speaking for myself, I prefer VHDL for the stricter declarations.

When were wire’s and reg’s declared the same in Verilog? Maybe it was before my time.

If you want to do something like:

always @*

a = b + c;

Even though ‘a’ is technically a wire and the above implements a combinatorial circuit, you still need to declare ‘a’ as ‘reg’, because it’s used in an assignment.

The ‘always @’ is what makes your example a register (and therefore requires reg a). If you want a combinatorial operation, Verilog has ‘assign’.

assign a = b + c;

I know, but assign can only handle expressions. Sometimes, the logic is more complex and you’d like to write it using a ‘case’ statement. In that case, you need the “always @”. But then you’d have to use reg instead of wire, even though it’s still implemented as combinatorial logic.

Just a heads up for those interested in watching Indie Game: The Movie, it’s on Netflix.

Lol, also seen it already. It was okay.

These guys are looking for a senior FPGA programmer. Supercomputers, simulation envirionments, FPGA, what could be more fun?

http://airstonelabs.com/