The Parallax Propeller is an interesting chip that doesn’t get a lot of love, but since the entire chip was released as open source, that might be about to change: people are putting this chip inside FPGA and modifying the binaries to give the chip functions that never existed in the original.

Last August, Parallax released the source for the P8X32A, giving anyone with an FPGA board the ability to try out the Prop for their own designs. Since then, a few people have put some time in, cleaning up the files, unscrambling ROM images, fixing bugs, and all the general maintenance that an open source microcontroller core requires.

[Sylwester] has grabbed some of the experimental changes found on the Parallax forum and included them as a branch of the Propeller source. There is support for a second 32-bit port, giving the new chip 64 I/O pins, multiply instructions, video generators, hard-coded SD card libraries, and a variant called a microProp that has four cores instead of eight.

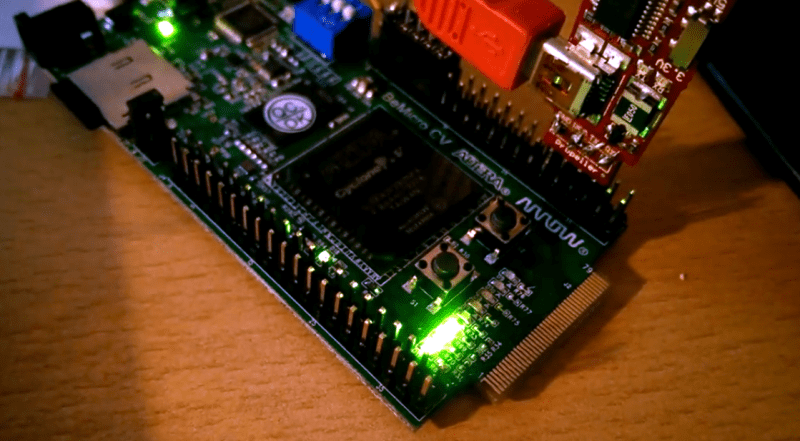

You can grab all the updated sources right here and load them up on a DE0 Nano FPGA board. If you’re exceptionally lucky and have the Altera DE2-115 dev board, you’ll also be able to run the upcoming Propeller 2.

Actually, [Sylwester]’s special features in his git repository at the “right here” link above will only work on the BeMicro CV at this time.

As [Sylwester] mentions on his website, I manage a Github repository at https://github.com/jacgoudsmit/P8X32A_Emulation where I track various changes proposed on the Propeller Verilog forum (http://forums.parallax.com/forumdisplay.php/101). By default, the sources from the Altera branch will compile with the free Quartus II Web Edition to something that essentially is a near-perfect emulation of the Propeller. Various features such as increased hub RAM can be enabled easily. The documentation is pretty much non-existent at this time because we’re still in spin-up stage (pun not intended).

I’m in the process of integrating the changes by [Sylwester] (aka [6581] aka [DataNoiseTV] aka [Syso]) in my 6581_Altera branch. They will be merged into the default Altera branch soon.

There are also sources for Xilinx FPGA’s, using the free ISE tool. Currently they are in a separate directory, but the plan is to change the directories so that the same Verilog sources including all the features can be used on both Xilinx as well as Altera FPGA’s.

Thanks for posting!

I think it’s a great tool for education, and a good way to experiment with the propeller architecture. However, for real applications, I doubt that the propeller is an efficient way to use the (expensive) resources of an FPGA. The strong point of the propeller is the flexibility to run peripherals in software. However, when you use an FPGA, you already have the flexibility to define your own peripherals in hardware, which will be faster and smaller.

There is a lot of code reuse in FPGA development. There is an entire industry of “IP cores” which implement various functionality very efficiently, so presumably you end up with islands of optimization separated by oceans of rush-jobs.

BTW, aliexpress seems to have a few Cyclone IV boards for a little over 40€. The Parallax forums say that you can run the Prop II on the Cyclone IV, but the Cyclone V better represents its full performance.

Perhaps the 4-core version of the Prop II is a nice compromise since Quartus II appears to do push-botton time/space tradeoff?

These boards have very small Cyclone IV, only around 5K LE, which is not too bad but I think the Prop would not fit.

Oops!The multiple ‘E’s and identical numbers tricked me. Thanks for the heads up. =)

In fact, my code will work on other boards (Altera & Xilinx), too. It will mostly only require some pin-mapping. The rest should just be working out of the box!

True, but “as is”, the code in your repo only worked for the BeMicro at the time the article was published. :-)

Don’t take it personal, I just wanted to warn potential users that your features aren’t done all the way for all targets yet.

smh

I would go and have a play with it if I knew if it would fit on the FPGA I have here. Cost’s nothing to load it in and try it.

I only have smaller Xilinx FPGA, Spartan 3E 200 and what ever is in the papilio one. I think it’s 500k.

The 3E500 may be big enough, if you reduce the amount of BRAM used (the report below shows over 600K bits used, the 3E500 only has 360K bits), and depending how comparable the compilers/equivalent LE counts are (supposedly the 500 is equivalent to about 10K LE).

On the Cyclones, the P1V takes up slightly less than 9000 LE’s if I remember correctly. It also uses 48KB RAM and up to 32KB ROM (ROM can be reduced to 4KB without losing most of the functionality).

Oh, I forgot, you can reduce the number of cogs to free up space, and we’ll be working on other ways to do that too (e.g. don’t put video and/or timer functionality in all cogs).

===Jac

Here is some logic utilization report:

https://git.no-route.org/syso/p8x32a_emulation/wikis/LogicUtilization

This is for the version without 64 I/O and without MUL/MULS.

Hello! Would it be possible to create a pin-compatible FPGA-based replacement for the original Propeller 1 in the 40-pin DIP housing (just in case Parallax discontinues the P1)? I have no experience with FPGAs and I don’t know whether they are available as DIP chips at all.