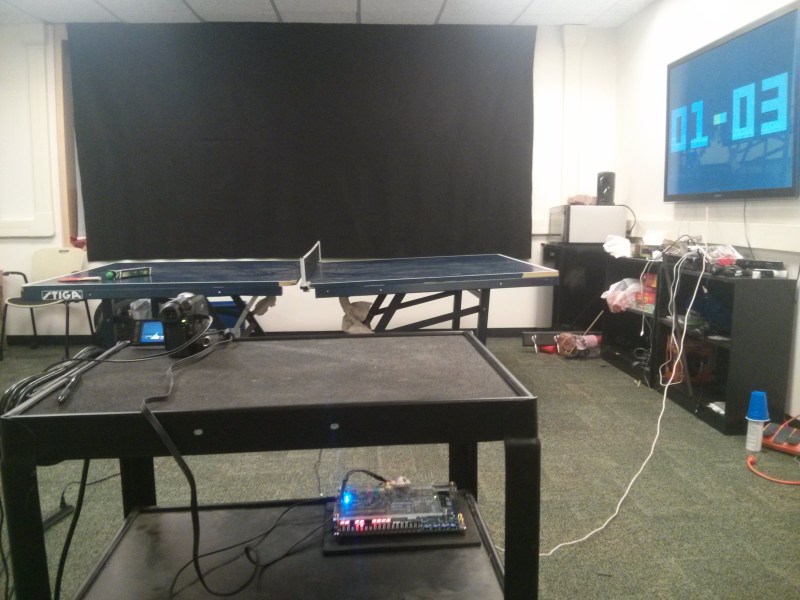

It’s graduation time, and you know what that means! Another great round of senior design projects doing things that are usually pretty unique. [Bruce Land] sent in a great one from Cornell where the students have been working on a project that uses FPGAs and a few video cameras to keep score of a ping-pong game.

The system works by processing a live NTSC feed of a ping pong game. The ball is painted a particular color to aid in detection, and the FPGAs that process the video can keep track of where the net is, how many times the ball bounces, and if the ball has been hit by a player. With all of this information, the system can keep track of the score of the game, which is displayed on a monitor near the table. Now, the players are free to concentrate on their game and don’t have to worry about keeping score!

This is a pretty impressive demonstration of FPGAs and video processing that has applications beyond just ping pong. What would you use it for? It’s always interesting to see what students are working on; core concepts from these experiments tend to make their way into their professional lives later on. Maybe they’ll even take this project to the next level and build an actual real, working ping pong robot to work with their scoring system!

That’s really impressive. I’ve only done some “Hello world” type VHDL/FPGA work so, bearing that in mind, how does this compare to doing it in software? I mean sure, doing it in hardware obviously makes it faster and could process several feeds at once, perhaps more efficiently than software.

But what I’m getting at is, in software you can use various API’s and frameworks to extract frames from a camera, do image processing, and all that fancy stuff, but with VHDL you would literally have to do all of that from scratch right? So basically this is a very complex project I suppose?

Using a CPU or GPU is certainly a lot easier, more flexible, and you can leverage many high quality libraries to get the job done. FPGAs are dedicated hardware, but theirs is probably running at 100 MHz, while a CPU might be running 25 or 30 times faster, allowing for a lot of relative inefficiency. A tuned FPGA implementation isn’t necessarily faster, just a lot more power efficient for this fixed task.

But that misses the point — their class is about learning how to use FPGAs, and in that regard, having a fun and creative problem to solve is great. This is a lot more fun than the projects I did 30 years ago in college.

In a real game the ball goes much much faster including slams. Can it detect that fast?

The limit is probably the FPS of the image sensor. Detecting a white blob on a black background can be done at almost any rate with an FPGA.

The limit of an fpga would be a mix of the FPS of the camera and the FPGAs ability to track a blurred ball

honestly going farther into what pingpong is about on a professional level would require an RTOS … probably windows or ubuntu on an i3 or higher XP

The camera is by far the primary limitation. With a high-speed camera FPGAs can definitely handle the speed of professional ping pong: https://www.youtube.com/watch?v=dmi_pwhYUvY

My sole dedication at this point in life is building multi node cluster of these amazing damn devices. Since FPGA’s are great at floating point I’m trying really hard to figure out what would be the “ideal” chip to maximize concurrent processing per node, I know (most) FPGA’s contain DSP slices but I’m trying to figure out if and WHAT would be the best optimization to call out to a FIXED point function off board chip layout for div sqrt or mult cube exponent.

Do I assign a SERDES to some sort of ECL/PECL type 64-bit ALU layout? Should I use a programmable DSP chip like a 700 class Blackfin? (I’d like the system to reflash itself once it finds a optimized Algo), I’m leaning on the Cortex-M7 but the only player available is ST… Atmel is in the works from what I understand.

“Pong dude”

Errr. Um. Eh, yeah. this is cool.