“RISC architecture is going to change everything”, which is why [SHAOS] is building this cool RISC-V DIY retro-style computer.

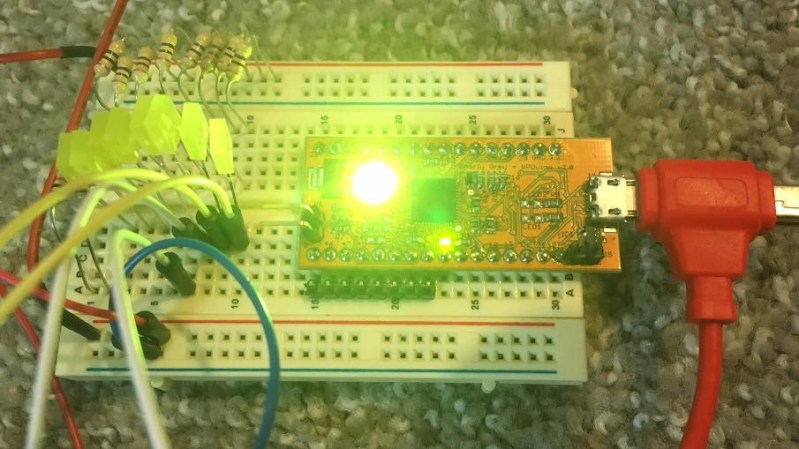

The project took inspiration from another hacker’s work in building a RISC-V emulator; shared in the Hackaday FPGA chat. He took it a bit further and got it going on an UPDuino v2.0 board which features a iCE40 FPGA from Lattice.

The board passes all the tests for the RISC-V subset he’s aiming for and even run some Zephry RTOS examples. He’s done a really good job of documenting how he got the code to run as well as many of the experiments he’s run so far. All the project files for ICEcube2 software are posted. It’s not the only RISC-V CPU we’ve seen in an FPGA, but the code is actually very clear and worth a read if you’re into such things.

We think anyone interested in duplicating his work could do so somewhat easily and start playing around with this increasingly popular architecture. Or at least get some LED’s blinking in an arcane but meaningful way. Video after the break.

Surely you mean implementing not emulating?

My exact same thought!

Our thought too. For some reason (maybe even language) it’s referred to in the original project as an “emulator”. But if you dig through retro.v, he’s clearly implementing the instruction set. I can’t think of any way to do so more literally!

This is a scratchbuilt RISC-V CPU and tiny SOC as soft core on an FPGA.

It’s a pretty cool project for that, too. Kudos, SHAOS.

Sorry for confusion – I started with emulator and used it to debug code and see how questionable parts of RISC-V ISA were implemented then I wrote my own Verilog implementation of RV32I from SCRATCH (main feature of it is 8-bit bus) and run it in Verilator (emulator of Verilog) and then put it inside iCE40 FPGA with LED as output and then TS-232.

A few corrections:

– it can pass MOST of compliance tests (not ALL) for example it doesn’t have any sense for me to throw unaligned memory access exception because my core can read/write 1,2 or 4 bytes from ANY address in memory (thanks to 8-bit “retro” bus);

– I was not able to run Zephir on it yet…

I meant RS-232 :)

RS = Recommend Standard is out of date as it has became TIA-232.

Serial communication through DB9 connector is out of date, so I will call it RS-232 forever ;)

It’s a neat project, that’s for sure.

An 8-bit data bus!

The 68008/8088 of the RISC-V world :)

As I understand it RISC-V allows un-aligned memory access. It doesn’t recommend it and it might be slow, but it’s not illegal. If you are doing the RV32C instructions then you have unaligned reads because of the 32/16 bit instruction mix. In any case, good job! I appear to be going down a similar path: https://github.com/deadsy/riscv

hi SHOUS ,

i designed a riscv-core by Migen ( hardware description langage ) i write in python and the tool generate verilog , i want now simulate my riscv core , so i find many tests in github open source , ( benchmarks ) , i install the repository of riscv-tests , and now i dont know how i run my riscv core with this test ?? its my first experience work in that thematics , and its the first time i work with linux ,, can you help me ; how i do !

If you have Verilog generated then you can use Verilator to compile C++ program that implements that Verilog description and then you can put some C++ code around to run compliance tests – I think I had some instructions how to do that in the logs of my project and some code in GitLab repo

“RISC architecture is going to change everything” – pretty sure I heard a similar line in 1995’s Hackers

I seem to remember that as well. Some of us are old enough to remember SPARC, MIPS and (Alpha) AXP.

And the even more obscure Ridge computer

RISC won. But it wasn’t a clean victory. x86 is CISC on the outside but RISC-y internally. ARM is nominally RISC, but has perhaps strayed from ideological purity as the ISA has been extended. MIPS, SPARC and PowerPC are fading, but I think that’s more related to business issues. The RISC-V ISA is interesting because it tries to learn from 30 years of ISA evolution not to repeat the mistakes of others. I think the Chinese will make RISC-V sucessful. It lets them save a buck on licensing and makes them less dependent on US controlled technology firms. RISCV is not a CPU innovation, it’s an IP innovation. It commodotizes the ISA in the same way that Linux commodotizes the OS.

Hey, I’ve got one of those UPDuino v2 boards! Maybe now I can finally take it out of its packaging and do something with it. 😂