If you want to use a display or camera with an FPGA, you will often end up with a MIPI-based solution. As of the Xilinx Vivado 2020.1 release, the MIPI DSI (display serial interface) and CSI (camera serial interface) IP blocks are now bundled with the IDE to be used freely with Xilinx FPGAs.

The Xilinx MIPI CSI2 receiver block implements the CSI-2 v1.1 specification, which although a bit older is essentially the same CSI implementation as on the Raspberry Pi boards. This means that it would allow one to use this IP block on an FPGA with many common CSI camera modules out there. The IP block offers a standard AXI4 interface for connecting up to the rest of a design.

Similarly, the Xilinx MIPI DSI transmitter block implements DSI v1.3 specification. This offers a maximum data rate of 1.5 Gbps, with an AXI4-lite interface to communicate with the rest of the design. Both IP blocks are subject to the Core license agreement, which doesn’t appear to preclude it from being used in a specific fashion, whether commercial or personal.

This is not the only way to use MIPI devices with an FPGA, of course. Take for example [Daveshah]’s CSRIx project on Github.

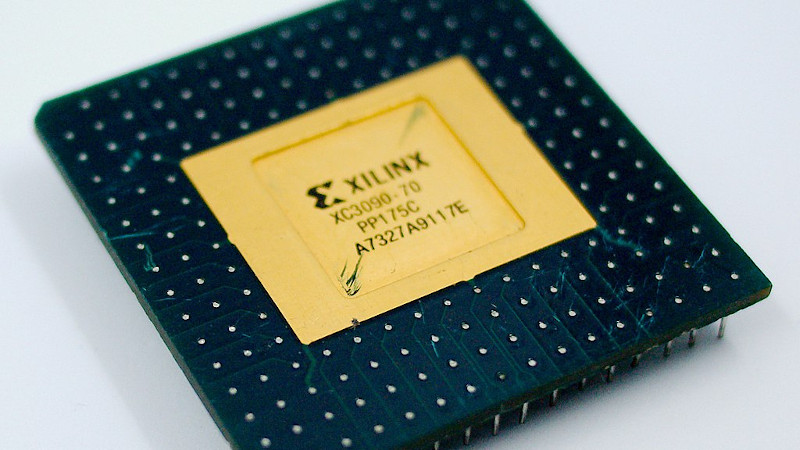

Header image: Kwapix / CC BY-SA 4.0

I find it interesting that the image is of a three decade old FPGA, that wouldn’t be able to fit the MIPI IP even if Vivado could be made to work on it.

LOL that was my first thought …Good that Xilinx have released the IP though …Should see some new toys based on it!

Yes, be happy with those drug dealers tactics (first shots on the house)

New ones aren’t as pretty LOL

Other ppl be like “bash it and smash it and boil it in acid… there’s $15 of gold in that shiz.”

What is the Altera cost for MIPI?

I have never had to implement a display with an FPGA before but i do want to play around with it

In my opinion DSI was a step backwards. Many DSI display controllers require initialization commands and some of them even need the MIPI lines to have a specific level during reset. Some use in-band commands to control the backlight, some use separate pins. They gave manufacturers an interface to send commands and the manufacturers abused it to save a few cents on an EEPROM that holds the display configuration.

In the good old days of 18/24 bit parallel and LVDS interfaces you just had to use the correct timings for an image to show up on the display.

Years ago I was working on AOSP-derivative firmware bringups for non-AOSP devices, including participating in Sony’s Open Devices project.

Getting display timings correct for some of the Xperia Z family (especially Z2/Z3) was a nightmare. Something in newer Qualcomm kernel baselines changed things such that timing settings in old DTBs would no longer work and needed retuning – I don’t know if anyone was ever able to figure out a setting that didn’t cause period weird glitches where the lower part of the display would be random garbage for a few frames.

Altera don’t have a MIPI IP and also don’t have DPhy comparable chip yet. So to use MIPI with Altera, you need external devices or some passive resistor network ( for slower speed) to connect MIPI to the chip.

I’d like to play around with this on a Spartan-7 board but the phy layer seems tricky… anybody know what’s necessary to support the phy layer on a spartan-7 device?

Yes, look up the xilinx doc XAPP894. You can apparently emulate a D-PHY with some resistors. Not certain that a Spartan 7 can do that, but look at that doc first.

SP701 based application example design available in https://www.xilinx.com/support/documentation/ip_documentation/mipi_csi2_rx_subsystem/v4_1/pg232-mipi-csi2-rx.pdf

As far as MIPI DSI goes, don’t miss Mike’s iPod Nano display interface reverse engineering videos:

https://www.youtube.com/watch?v=7TedIzmguP0

Not an open source license. Not worth looking at.

Yeah, not open source. A waste of time. Just design your own instead.

The CSI is actually against the “Controller Subsystems” which is quite interesting because it looks as though it’s not just the Rx IP – but the Tx Controller as well. Which allows for a possible lump-in-the-line unit to modify video data before passing it on to something else that’s not as fast/intelligent or maybe send a custom data stream directly into a RPi?

I really would love to see an open-source CSI multiplexer.

(CSI supports multiplexing using, if I recall correctly, some sort of device tagging or virtual channels, such that multiple camera sensors can share a single CSI interface. Many FPD-Link/GMSL SERDES units support this, but there are applications where I’d like to have 4-8 or more sensors feeding a single NVidia Jetson, without the “analog switch matrix” hacks that some CSI mux solutions use. Most notably, a 360-degree/surround camera.)

The Jetson has 6 MIPI CSI receivers so you can do that today. It’s not switched but you need a breakout board (e.g. Leopard Imaging) to connect them up.

Nah, c’mon, you love 4066s really.

PG232 of Xilinx MIPI CSI-2 Rx Subsystem specifies CSI-2 version is v2.0, while the post specifies a different version.

https://www.xilinx.com/support/documentation/ip_documentation/mipi_csi2_rx_subsystem/v4_1/pg232-mipi-csi2-rx.pdf

Lattice Crosslink devices were sorta special built for these use cases…