FPGAs, CPLDs, PALs, and GALs, Oh My! This week’s Hacklet focuses on some of the best Programmable Logic projects on Hackaday.io! Programmable logic devices tend to have a steep learning curve. Not only is a new hacker learning complex parts, but there are entire new languages to learn – like VHDL or Verilog. Taking the plunge and jumping in to programmable logic is well worth it though. High-speed projects which would be impossible with microcontrollers are suddenly within reach!

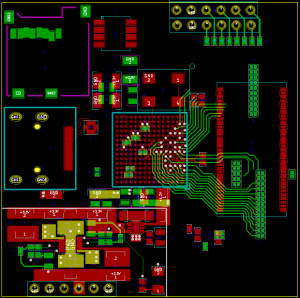

A great example of this is [Tom McLeod’s] Cheap FPGA-based HDMI Experimenting Board. [Tom’s] goal was to create a board which could output 720p video via HDMI at a reasonable frame rate. He’s using a Xilinx Spartan 6 chip to do it, along with a handful of support components. The images will be stored on an SD card. [Tom] is hoping to do some video with the setup as well, but he has yet to see if the chip will be fast enough to handle video decoding while generating the HDMI data stream. [Tom] has been quiet on this project for a few months – so we’re hoping that either he will see this post and send an update, or that someone will pick up his source files and continue the project!

A great example of this is [Tom McLeod’s] Cheap FPGA-based HDMI Experimenting Board. [Tom’s] goal was to create a board which could output 720p video via HDMI at a reasonable frame rate. He’s using a Xilinx Spartan 6 chip to do it, along with a handful of support components. The images will be stored on an SD card. [Tom] is hoping to do some video with the setup as well, but he has yet to see if the chip will be fast enough to handle video decoding while generating the HDMI data stream. [Tom] has been quiet on this project for a few months – so we’re hoping that either he will see this post and send an update, or that someone will pick up his source files and continue the project!

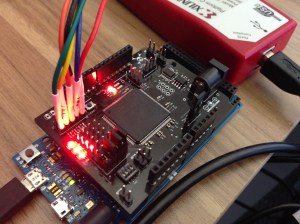

Next up is our own [technolomaniac] with his Arduino-Compatible FPGA Shield. Starting out with FPGAs can be difficult. [Technolomaniac] has made it a bit easier with this shield. Originally started as a project on .io and now available in The Hackaday Store, the shield features a Xilinx Spartan 6 FPGA. [Technolomaniac] made power and interfacing easy by including regulators and level shifters to keep the sensitive FPGA happy. Not sure where to start? Check out [Mike Szczys’] Spartan-6 FPGA Hello World! [Mike] takes us from installing Xilinx’s free tool chain to getting a “hello world” led blinker running!

Next up is our own [technolomaniac] with his Arduino-Compatible FPGA Shield. Starting out with FPGAs can be difficult. [Technolomaniac] has made it a bit easier with this shield. Originally started as a project on .io and now available in The Hackaday Store, the shield features a Xilinx Spartan 6 FPGA. [Technolomaniac] made power and interfacing easy by including regulators and level shifters to keep the sensitive FPGA happy. Not sure where to start? Check out [Mike Szczys’] Spartan-6 FPGA Hello World! [Mike] takes us from installing Xilinx’s free tool chain to getting a “hello world” led blinker running!

Still interested in learning about Programmable Logic, but not sure where to go? Check out [Bruce Land’s] Teaching FPGA parallel computing. Actually, check out everything [Bruce] has done on Hackaday.io – the man is a living legend, and a wealth of information on electronics and embedded systems. Being a professor of engineering at New York’s Cornell University doesn’t hurt either! In Teaching FPGA parallel computing, [Bruce] links to Cornell’s ECE 5760 class, which he instructs. The class uses an Altera/Terasic DE2 FPGA board to demonstrate parallel computing using programmable logic devices. Note that [Bruce] teaches this class using Verilog, so all you seasoned VHDL folks still can learn something new!

Still interested in learning about Programmable Logic, but not sure where to go? Check out [Bruce Land’s] Teaching FPGA parallel computing. Actually, check out everything [Bruce] has done on Hackaday.io – the man is a living legend, and a wealth of information on electronics and embedded systems. Being a professor of engineering at New York’s Cornell University doesn’t hurt either! In Teaching FPGA parallel computing, [Bruce] links to Cornell’s ECE 5760 class, which he instructs. The class uses an Altera/Terasic DE2 FPGA board to demonstrate parallel computing using programmable logic devices. Note that [Bruce] teaches this class using Verilog, so all you seasoned VHDL folks still can learn something new!

Finally, we have [Michael A. Morris] with Chameleon. Chameleon is an Arduino compatible FPGA board with a Xilinx Spartan 3A FPGA on-board. [Michael] designed Chameleon for two major purposes: soft-core processors, and intelligent serial communications interface. On the processor side Chameleon really shines. [Michael] has implemented a 6502 core in his design. This means that it would be right at home as the core of a retrocomputing project. [Michael] is still hard at work on Chameleon, he’s recently gotten fig-FORTH 1.0 running! Nice work [Michael]!

Finally, we have [Michael A. Morris] with Chameleon. Chameleon is an Arduino compatible FPGA board with a Xilinx Spartan 3A FPGA on-board. [Michael] designed Chameleon for two major purposes: soft-core processors, and intelligent serial communications interface. On the processor side Chameleon really shines. [Michael] has implemented a 6502 core in his design. This means that it would be right at home as the core of a retrocomputing project. [Michael] is still hard at work on Chameleon, he’s recently gotten fig-FORTH 1.0 running! Nice work [Michael]!

Want more programmable logic goodness? Check out our Programmable Logic List!

That about wraps things up for this episode of The Hacklet! As always, see you next week. Same hack time, same hack channel, bringing you the best of Hackaday.io!

Take a look at this one, i am waiting for it now should have it soon.

https://www.kickstarter.com/projects/13588168/papilio-duo-drag-and-drop-fpga-circuit-lab-for-mak

Forgot the link..

Wow, this board actually uses SRAM rather than SD RAM like all the others. SRAM is much easier to interface to so it’s ideal for learners (like me). I have a Papilio One which is the Xilinx Spartan 3 chip, no RAM and no PLL clock synthesis. I am just going to make a SRAM wing for it.

I meant “no *external* RAM”. It still has about 40K internal Block RAM.

I saw that one, but this looks more interesting, and is cheaper.

http://www.scarabhardware.com/minispartan6/

It’s available with LX9 or LX25 FPGAs, comes with twin HDMI ports (input and output) and has 64 GPIO ports.

I have both the pappilio duo aswell as the scarabon my ‘to receive list’. Haven’t received them yet. But the Scarab ide is still nog released :(

That was a reference to “lions and tigers and bears, oh my!” from the Wizard of Oz, you pedantic little infant.

Thanks, DainBramage! At least someone got it :)

My pleasure. :D

Those lectures of his on Youtube really are a great asset to us all. e.g. I would probably not have found out that cellular automata on FPGAs are a ‘thing’ without those lectures, and how this… ‘monad’, if you’ll idulge me, is a near perfect study case for something fundamental. Not sure if computability alone defines it…

Hardware is the least of the issues for someone trying to get into FPGA.

It really doesn’t matter what you choose for learning hardware except that you are choosing a manufacture and locking yourself into their development software. As for hardware, I think the simpler it is the better.

I have learnt more using a 72 macrocell Xilinx CPLD than using a 500K gate Xilinx Spartan 3 development board. The Spartan 3 development board and wing was $100 and the CPLD board was $15.

Having been burnt in the past by buying development boards only to find they’re next to useless due to poor documentation. I chose the Papilio One 500K and LogicStart MegaWing to learn on. It had tutorials specifically written for the board so I went with that.

The Papilio board / wing is very good in that it has a range of gadgets to play with but I found the tutorials were lacking. When I went to find better tutorials, I found that most of them don’t cover what I needed to learn so it’s not a bad aspect about the Papilio, it’s just how things are.

As an experienced programmer what I most need to know about a new language is where the commas, brackets, semicolons go and what is the general ‘structure’ of the language. VHDL is a right pain in this regard as it has unusual syntax rules and the structure is elusive at first.

The problems of learning a new syntax / structure are compounded by the Xilinx ISE design environment. The code editor is nothing more than a text editor with a splattering of highlighting for primitives. The very little highlighting it has is exceptionally poor and has no context. To compound matters even more, error messages come from individual components of the tool chain so without knowing what each tool chain component actually does, you have no ‘context’ for the error message rendering it more cryptic than the windows BSOD error screen.

The solution for me was to install an external code editor. I installed a trial version of Sigasi. It’s more that just a code editor. It will auto suggest keywords that are specifically in ‘context’ with your written code. It also shows errors in the code immediately so you don’t have to deal with as many cryptic error messages from the Xilinx tool chain. This made all the difference between not understanding the structure and writing complex code with ease. I am not in any way associated with Sigasi.

There may be other good code editors out there and I would love to hear from others.

Once again, for hardware – all you need is a ‘constraints’ file, a decent schematic and of course a JTAG port and programmer. Simple and cheep is better. Save your money to buy the better board when you know how to choose what is better for you. Xilinx JTAG programmers are about $40 and Altera programmers are about $5. I haven’t tried any Altera products yet. There are many cheap (under $20) CPLD and small FPGA development boards on ebay that are suitable for beginners. Just make sure you have the right programmer:board combination, schematic and constraints file.

Sorry for the long post but I was hoping that i may save someone some hair loss.

Agreed, I have seen many beginners agonize over stupid and pointless discussions like the best beginner FPGA board… It Doesn’t Matter(TM)

The dev board will not solve the work of actually learning hardware. Learning structures, algorithms, even simple things like semaphores and passing DMA data between clock domains.

It takes a while plugging away to finally start to understand how to effectively use HDL and do “hardware” proper. The iteration time is longer.

But while we’re bringing up devboards, let me plug for any Altera board. Why? Free Signaltap ILA. That alone is a HUGE reason to not be using xilinx (Chipscope requires a subscription).

If you don’t know what an ILA is, it’s basically a black box logic analyzer you wire into your design and cook into the bitstream. You can probe any point in your HDL and see how it works.

This is absolutely essential! Simulation does not work for everything.

There is some vendor lock in, but not so much as Xilinx/Altera/Lattice pretty much have similar “flow” process of compiling/simulate/fitting/post fit timing etc.

I found verilog is a bit easier because of its c-ish syntax. (I actually learn VHDL first.) I got a quick reference booklet and a book for VHDL, but I use online website to look up syntax.

You can use the development environment GUI to create a constraint file for the pinout. It is drag & drop, but you’ll need to have the top level design first.

It would be nice if there is a way of automating Eagle CAD schematic to extracting constraint files. For now, I extracted the netlist, imported into Excel, sorted and formatted them into constrain file.

Great post Rob! You hit the nail on the head as far as starting goes. I cut my teeth many years ago on the 22V10 chip, and I wish it was still around to help people get a start with programmable logic. CPLDs are the closest thing we have.

On the FPGA side, check out the Xula2 – Yes, we carry it in the store, but that’s because I really like what [Dave] has done. He’s got a whole (free) book on his website at http://www.xess.com/ called “FPGA?, Now What!?!” which takes you through the learning curve.

That’s interesting because the CPLD I have been using (Xilinx XC9572XL) is based on 22V10’s as function blocks. Think it has 4 x 22V10’s on a die with more interconnect for between the blocks and some global signals.

I actually have a stick of about 20 22V10’s here as well. I don’t know what they will ever be used for now as they’re so small. Perhaps a repair or where small 5 Volt CPLD is needed.

I have downloaded the tutorial and I will have a read later.

I am not so keen on the Xula2 (as a beginner) because the SD RAM will push me into copying a pre-made SD RAM interface rather than making my own. There are too many hurdles with SD RAM for a beginner. I would much favor a board with SRAM that encourages me to write the interface myself. I will be making a SRAM wing or shield for my Papilio One and CPLD board as that seems the easier way for me.

I see that Papilio has released a Papilio Due with SRAM. Unfortunately they changed the physical layout so the older shields or wings wont fit so I still think the Papiolio One is the better of the Papilios for a beginner to intermediate. It has 20K to 40K of internal Block RAM (BRAM) anyway.

22V10 are still around. There are what looks like Atmel’s 22V10 on cheap BIOS Diag cards from China. Unlike modern day CPLD, they are a pain to program – need a programmer. I got a few tubes gathering dust. National’s GAL6001 MAPL, Lattice ispLSI etc. generation of parts were a much closer descendant of the GAL.

Crazy enough I managed to have VHDL and state machines to compile into 22V10 efficiently as my on the job self training. It was an good exercise to learn/adjust my coding style and how it is compiled to gate/macrocell level to exactly what I want. I do the same for C code for 8-bit uC to get a feel on the c compiler.

As for SDRAM, prerequisite: state machines, combinational logic, buses, muxes, interfacing timing, test bench.

A good starting point is to understand how SDRAM works (from datasheet), then map out a state machine. I was also using a timing design package and figure out how the external timing part (wait states, nops etc) should be. From there, either use the state machine entry tool in the environment or if you like typing it out in HDL. Then it is pretty straight forward as you feed in the SDRAM control signals/address lines in the various states. Generating a testbench for your controller take a bit of work. A very detail timing accurate SDRAM simulation model is available from Micron(?).

Indeed they do. I still use 16v8, 20v8 and 22v10 in some designs now – glue logic mostly, like external decoders and latches for an Atmel AVR 328P. I have an ancient All-11P programmer, which works under WINE so I don’t have to use Windows. I’ve moved on from using Abel to program them as I did in the distant past – now I use the Lattice ispLever Classic software (which also runs in WINE) and I write in Verilog. eBay is a good place to pick up tubes of NOS parts when someone is clearing out – I have more than enough now to see me to Silicon Heaven.

[Adam Fabio] Can you please add my hackaday.io project to the “Programmable Logic List”?

http://hackaday.io/project/1347-fpga-computereval-board

Done! Sorry for the oversight!

Don’t forget hamster and his links and ‘course’. I hope he publishes V2 one day, or does a course – i’d go.

http://hamsterworks.co.nz/mediawiki/index.php/Main_Page

There is also http://www.fpga4fun.com/ with sample projects and tutorials.