Field Programmable Gate Arrays (FPGAs) let you program any logic you’d like onto a chip. You write your logic using a hardware description language, then flash it to the FPGA. You can even design your own processor and flash it to the chip.

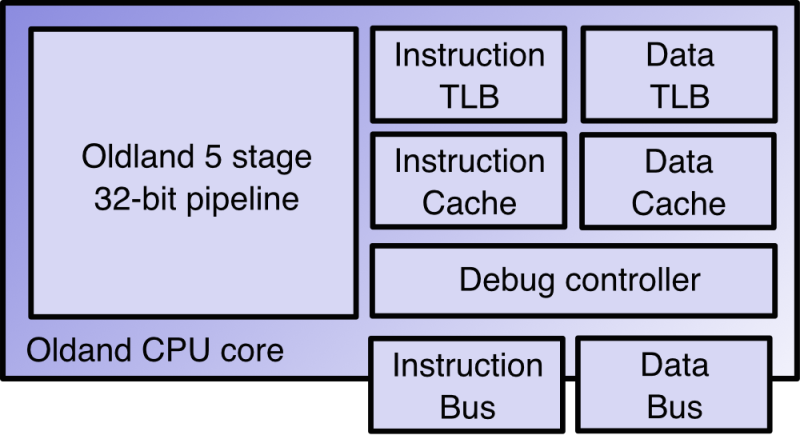

That’s exactly what [jamieiles] has done with the Oldland CPU. It’s an open source 32 bit CPU core that you can synthesize for use on an FPGA. Not only can you browse through all the Verilog code in the Github repo, but there’s also a bunch of tools for working with this CPU core.

Included with the package is oldland-rtlsim, which lets you simulate the processor on a PC. The oldland-debug tool lets you connect to the processor for programming and debugging over JTAG. Finally, there’s a GNU toolchain port that lets you build C code for the device.

Going one step futher, [jamieiles] built a full SoC around the Oldland core. This has SPI, UART, timers, and more features you’d expect to find in a microcontroller. It can be flashed to the relatively cheap Terasic DE0-Nano board.

[jamieiles] has also ported u-boot to the processor, and the next thing on the list is the Linux kernel. If you’ve ever been interested in how CPUs actually work, this is a neat project to look through. If you want more open source CPU cores, check out OpenCores.

Wow that looks awesome!

once i programmed a brainfuck cpu. wasnt synthesizable because of missing a practical ram and other things, but the simulation ran successfully on http://www.99-bottles-of-beer.net/language-brainfuck-2542.html.

“You write your logic using a hardware description language, then flash it to the FPGA”

Well, most FPGA’s are not flashed (they don’t have flash). Majority of them are configured from an external flash/rom/micro, etc. at each power up.

Very impressive project. Apparently you can run this at 75Mhz on a De0 Nano board. Definitely not bad for a soft 32 bit cpu. Kudos to him.

I wish he had a blog, too. Would be nice to see the progress of it coming along.

Thanks for taking a look! I haven’t been great at blogging in the past, but I do have blog.jamieiles.com and I’ll try to document my progress in the future!

This is a really nice implementation, I like the Keynsham SoC loadout for UART/SPI Master/IRQ Controller. Check out “RISC-V” for a really beefy 32-bit chip.