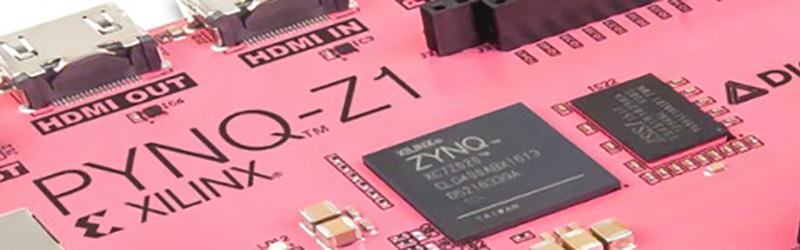

FPGAs are the future, and there’s a chip out there that brings us the future today. I speak, of course, of the Xilinx Zynq, a combination of a high-power ARM A9 processor and a very capable FPGA. Now the Zynq has been made Pynq with a new dev board from Digilent.

The heart of this board, is, of course, the Xilinx Zynq packing a Dual-core ARM Cortex A9 processor and an FPGA with 1.3 Million reconfigurable gates. This is a dev board, though, and with that comes memory and peripherals. To the board, Digilent added 512MB of DDR3 RAM, a microSD slot, HDMI in and out, Ethernet, USB host, and GPIOs, some of which match the standard Arduino configuration.

This isn’t the first Zynq board out there by any measure. Last year, [antti] had a lot of fun with the Zynq and created the ZynqBerry, a Zynq in a Raspberry Pi form factor, and a Zynq Arduino shield. Barring that, we’ve seen the Zynq in a few research projects, but not so much in a basic dev board. The Pynq Zynq is among the first that will be produced in massive quantities.

There is, of course, one downside to the Pynq Zynq, and that is the price. It’s $229 USD, or $65 with an educational discount. That’s actually not that bad for what you’re getting. FPGAs will always be more expensive than an SoC stolen from a router or cell phone, no matter how powerful it is. That said, putting a powerful ARM processor and a hefty FPGA in a single package is an interesting proposition. Adding HDMI in and out even more so. Already we’ve seen a few interesting applications of the Zynq like synthesizers, quadcopters, and all of British radio. With this new board, hopefully a few enterprising FPGA gurus will pick one up and tell the rest of us mere mortals how to do some really cool stuff.

“Pynq with a new dev board from Diglent” Digilent

“packing a Dual-core AARM Cortex” ARM

” To the board, Diglent added” Digilent again

I’ve probably missed something so would you proof read again?

Fixd

“Fixd” Fixed

I see you’ve done your due digilence.

(I was joking)

Well, others have already tried this, selling microcontrollers with integrated FPGAs.

They all failed, so what is different this time?

The CPUs on these FPGAs aren’t microcontrollers, they are full-blown processors that are capable of running Linux. For some basic comparison, think Raspberry Pi with a million programmable gates to do with which you please. The Arduino shield compatible layout isn’t indicative of a microcontroller being onboard. Also, Intel (Altera’s new owner) doesn’t seem to think the CPU/FPGA combination is going away. They have Cyclone SoCs (similar to the Zynq), Arria SoCs, and I believe Stratix SoCs, even some Xeon CPUs have FPGA cores integrated/along side. The combination of these two technologies is really quite powerful for certain applications.

Still they are missing a GPU. I wish there is a SBC with a triple CPU/GPU/FPGA at an affordable price. The Zynq Ultra + which is probably the only solution I heard about to include a GPU is too much expensive up to now.

There are plenty of FPGA application which are coding a CPU in the FPGA, is called a soft core CPU. Now almost any manufacturer have realized that is better to put some “hard” (against “soft”) peripherals like I2C, SPI and even ARM cores. This technology is very appreciated since you can save a lot of logic in your FPGA, and as far as I know, those kind of FPGAs are in the market for while.

Your example with CPU with FPGA, is not used a lot because you would have a very small FPGA, and nowadays costs less to have a small “discrete” FPGA with a standard (so low cost) CPU.

PS: to be honest, this price is a ROBBERY….. copared to any kind of FPGA dev board manufactured directly from Altera, Xilinx and other less famous that I can’t recall right now.

I buy Fpga dev boards pretty often for work, and I typically pay a few thousand dollars a board.

The Terasic DE0 Nano SoC – Cyclone V SE FPGA, 1GB of DDR3 RAM, Twin 925MHz ARM A9 cores, Arduino compatible headers, ADC, Gigabit Ethernet, 2 x 40 pin GPIOs. Cost $99, or $90 with academic discount. You were saying?

Upper end FPGA boards with high speed tranceivers and shed loads of logic resources may set you back thousands, but this board isn’t competing in those leagues.

He was saying that “I buy Fpga dev boards pretty often for work, and I typically pay a few thousand dollars a board”.

But what was replied to was the claim that $229 was robbery – which is ludicrous. Even comparing with your example is something a bit over twice as expensive robbery given what FPGA boards go for? I think not.

BTW it could be worth it comparing the specifications between those two boards, the Pynq have HDMI I/O, audio I/O

etc. and the FPGA part is larger than your comparison board…

It’s implementing “Python productivity for Zynq”, essentially allowing a shift up in programming abstraction that can greatly increase productivity.

It also has an integrated web interface through which you can program it.

https://media.readthedocs.org/pdf/pynq/latest/pynq.pdf

In other words it’s really neat and I want one.

> there’s a chip out there that brings us the future today. I speak, of course, of the Xilinx Zynq

Two things:

1. The Zynq is what, 6 years available now? There’s not much “new” to learn these days. Open-Source Zynq projects are abundant, as is knowledge on the limitations and possibilities of the Zynq – which, basically, boils down to “nice, now I have an FPGA that is too small to do heavy lifting attached to a CPU that is too slow for the things that I’d use an FPGA for.” Still. Like the last years. The ARM hasn’t gotten any faster.

2. Seriously, this is really really uncomfortable to read in it’s current wording. I appreciate the writership, but this just feels like you’re the PR department of Xilinx.

You’re right Marcus, thanks for pointing these out. In the past months, many readers have expressed their regrets that more and more Hackaday’s blog entries adopt this “shiny, exciting and new” advertising-like writing style (and the false assumptions it often brings with it) but it seems to be a deliberate choice from editors.

Sad, but I’m still happy to find articles on these subjects here, just filtering out Gerrit Coetzee’s dumb clickbaits and adopting the old Slashdot habits to not pay much attention to TFA’s content, the real substance, better checked facts, and interesting exchange of arguments are likely to be found in the comments, which still are mostly uncensored (another deliberate but welcome choice from editors that helps to counterbalance the former).

“Seriously, this is really really uncomfortable to read in it’s current wording.”

Seriously, this is really really uncomfortable to read in its current wording.

“FPGA with 1.3 Million reconfigurable gates”

The ZYNQ XC7Z020-1CLG400C found on the board has 85k logic cells. Unless they somehow added the special use RAM and DSP slices to reach 1.3M gates.

A single Xilinx LE is worth a fair bit more than one gate equivalent.

It’s partly Xilinx’s fault, they liked to quote their FPGA capacities in gates. Even using the more standard LE count on their newer devices doesn’t give you the full picture. Resources like BRAM, DSP blocks etc are at least as important.

Just thinking about this on the way this morning. If I told the world my FPGA had 1.3M gates, sounds impressive. If each of those logic blocks was 100k gates each, saying I had 10 logic blocks would not impress anyone.

That’s obviously an extreme and contrived example, there’s no way a logic block would need that many gates, you can see why marketing latched onto that number rather than the others out there, it’s a “bigger” number.

“X is the future” is such a tired old statement. You do FPGAs injustice and lack creativity. Maybe try goin retro

There is already too much retro in Hackaday. :-) Think of all that nixie stuff – completely outdated in my opinion as we have LCD and OLED or all this “discreet processor/computer” efforts. Although this “…the future” statements are ‘dangerous’ :-) and FPGAs sure have there applications.

I think there is a SATA IP core that will work on that chip too, does anyone have a full list of cores that are known to be compatible?

7020s don’t have high speed transceivers

https://www.xilinx.com/products/silicon-devices/soc/zynq-7000.html#productTable.

So what SATA level can they do?

As far as I know, none. SATA 1.0 needs 1.5Gbps. The GPIO pins won’t get anywhere near that.

It would be nice if any of these boards exposed the high-speed interconnects using something like a standard FPGA Mezzanine Connector (using those devices in the Zynq family that do have the high-speed transceivers).

The picozed board is available with a 7015. At around $270 it’s not cheap.

I doubt there’s anything cheaper out there in the FMC league. (Is there?)

As long as the bitstream format for FPGA is kept confidential I will not use them. It could start to become interesting if tools to reconfigure the logic could run on the embedded platform, but with the current status of documentation, FPGA technology is mere a missed opportunity.

In that regard, projects like IceStorm have been a game changer for me… at work I sometimes have to grapple with someone else’s proprietary software or binary. I spend long hours dealing with such issues.

When I go home, the last thing I want to deal with is some proprietary piece of bloaty and expensive software just to generate a few kB of bitstream for configuring an FPGA or programming a microcontroller.

I’m in this to learn, so a big IP core library is not terribly interesting to me. I have limited time, so no time for fussing around with license keys or trying to figure out your proprietary blob.

I tried playing with an Altera FPGA at uni… and gave up because I could not get the Quartus II software to work even after jumping through Altera’s licensing hoops. (License to my machine? Errm, excuse me, it isn’t my FPGA board, and the university does not own my laptop!)

I have a Lattice ICE40HX8K board now thanks to IceStorm. I plan to do a memory controller with it, so need the pins that board offers. (The IceStick is just a little limited for that. The HX8K board using a 1K chip would have been perfect.)

I’d love to see more FPGAs in SOIC and DIP format, or smaller TQFP: I’m sure there are others that just want a handful of pins (14-28 pins), and while the IceStick is a good start, a DIP packaged equivalent would take up a lot less space.

As for the Zynq: love the idea, but at the moment the idea of needing a proprietary toolchain and OS to configure the FPGA side of it is what keeps me away. Release an open-source bare-bones toolchain like IceStorm, and maybe Xilinx might have something I’ll consider.

I like that.

good point

Hell, just release a Zynq specific build toolchain that runs on – the Zynq.

As it stands, it’s like demanding every Linux app be written in a version of Eclipse that ONLY runs on a Windows PC.

Proprietary toolchain? Yes (when talking about the fabric, the arm portion uses gcc).

Proprietary OS? Last i checked, Linux wasn’t proprietary. I do all my Xilinx development under Linux.

With these things, needing Windows is not uncommon. In my case with the Altera FPGA, I could get somewhere with the Windows version of Quartus II in that it at least tried to do something.

The Linux version flatly refused to work at all. I don’t recall the details as this was some 8 years ago. I recall just wanting a NIOS II softcore loaded so that I could get µClinux running to drive a LED display. Nothing fancy, and the FPGA board was what was kicking around for us to work with.

Given this experience, even if Xilinx tools did allegedly come in a Linux version, you can forgive my scepticism about them working properly or not.

There’s no “allegedly” about it. Xilinx tools have come in Linux form for at least a decade. Total tool chain. In fact, the Windows versions have always seemed more of a “port” to me than the Linux ones. I’m not sure which actually came first.

I work at a large company that uses a lot of FPGAs, and most of the FPGA devs that I see are doing most of their builds under Linux.

Xilinx runs faster linux. Windows ver operates on linux emulator. keep facts straight. have enough problems with fake USA/EU news.

“FPGAs in DIP format”

Realistically, learn to embrace modern packages.

Never! I can’t hand-solder good enough.

Any QFP is easily hand soldered. You do not need to solder each pin of a 0,5mm pitch device separately. Use plenty of flux and a drop of molten solder which you draw along the pins. Remove excess with solder wick. Did not use DIP or similar packages for years.

DIP may be unrealistic, but what about FPGAs in packages it is POSSIBLE to hand solder? Anything that’s only available in BGA is pretty much off my radar.

Altera’s Max 10 has a 144 EQFP that you can solder.

The zynq has a steep learning curve. I’ve been using it at work for about a year and am finally feeling like I can really do something with it.

The hard part i’ve found is not writing your little VHDL widget in the PL side. Its getting data to and from your widget to the PS side. Once you get over that hump the ARM+FPGA fabric really nice to have. I can use c to handle things like talking to a SPI LCD touchscreen, read and write to an SD card. Things that would require a crazy long state machines…. And use the PL fabric for multiple VHDL serial receivers that take data and cram it into BRAM for the PS to grab at its leisure.

Well, if you can make a BGA stay put on a bread board, I’d love to see it.

“Modern packages” for me means month-long waits for boards to come back from fabrication (since the track-work is too fine for me to achieve with the tools I have at home) and a very hit-and-miss affair soldering the little buggers.

The finer the pitch, the harder it gets. Some fabrication houses won’t do boards reliably for the finer BGA packages, and Lattice seems to love the really tiny ones!

Just the same, consider how many pins you’re limited to when you say “DIP”. The highest pin count I’ve ever seen in DIP (or SOIC) I think was 64 pins. Projects that need high gate counts generally also need a lot of I/O.

For the price, I prefer the Snickerdoodle. (http://krtkl.com) The connectors are a bit unusual, but they’re rated for high throughput, and there are a number of baseboards available. And you can easily interface it to your own custom board.

What is interesting in this more the integration of Pynq software/firmware, a Python access to FPGA modules, than the board itself. There are some equivalent board for while and Digilent just announce another very similar board https://blog.digilentinc.com/zynq-for-makers-introducing-the-arty-z7/.

I’m also preferring SnickerDoodle.from Krtkl.com. I intend to port Pynq on that board.

Not mentioned in the article; the PYNQ-Z1 board supports the PYNQ (Python on Zynq) open source project. http://www.pynq.io code here: http://www.github.com/xilinx/pynq docs here: pynq.readthedocs.io

SD Card image provided allows you to programming the board in Python out-of-the box using only a web browser.