We often think that not enough people are building things with FPGAs. We also love the retrotechtacular posts on old computer hardware. So it was hard to pass up [karlwoodward’s] post about the Chip Hack EDSAC Challenge — part of the 2017 Wuthering Bytes festival.

You might recognize EDSAC as what was arguably the first operational computer if you define a computer as what we think of today as a computer. [Maurice Wilkes] and his team invented a lot of things we take for granted today including subroutines (Wheeler jumps named after a graduate student).

The point to the EDSAC challenge was to expose people to creating designs with FPGAs, particularly using the Verilog hardware description language (HDL). If you want to follow along or run your own Chip Hack, the materials are available on the Web. You can see an FPGA driving a tape punch to create souvenir tapes in the video, below.

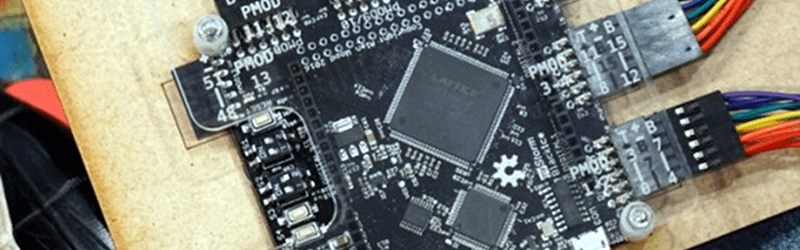

Some of the exercises are pretty simple and that’s perfect if you are starting out. The challenge uses a board with a Lattice ice40 FPGA and the open source toolchain for Lattice we’ve covered before. In fact, we’ve even done our own tutorials on the same basic device (but not the same board). Our final project generated PWM, not paper tape.

For the record, EDSAC was awesome. The execution unit was serial and processed bits that marched in one at a time over a mercury delay line. There is quite a bit of documentation and even some simulators, so if you ever wanted to get your hands into an old computer, this one isn’t a bad one to try.

Nice, but isn’t user accessible FPGAs coming to more desktops in the form of CPU/GPUs, not to mention what one can stick in a chipset, or wireless.

No, that would be simulation or emulation at best. At worst you are talking about microcode which is macro scale in comparison.

No? Why would Intel have any reason to start including user-accessible macrocells on its CPUs, and why would AMD or NVidia have any reason to do the same with their GPUs, especially when custom multi-core ASICs give *way* better performance for the tasks that, y’know, GPUs are designed for?

Like, are the executives at Intel, NVidia and AMD going to suddenly go on some coke-fueled bender, and at the end of it, go, “You know what we need to do? Spend millions or billions upending our design processes in order to put an incredibly niche feature in our chips in order to make a handful of hardware hackers happy”?

Actually Intel works on line of Xenon processors bundled with FPGA and also on a FPGA accelerator card. This is supposed to be used in large datacenters where the whole system is tuned to a specific workload though. So no, we will not see these in desktops, but you will probably be able to buy such hardware in a year or two.

You’ve not been paying attention then?

https://www.theregister.co.uk/2016/03/14/intel_xeon_fpga/

Too sad they choose blackice board as it’s quite the boutique-like fpga board (produced in batches only, sale advertised on a forum post).

While it may be a boutique, it is a fantastic fpga icestorm is a fantastic tool chain and doesn’t needs gigs of data.

I attended the conference and know the troubles with the wifi and the troubles of pulling down packages then you’ll run into issues.

The fact we got to meet and talk to ken who designed the boards was a plus point, ciifford wolf gave a talk aswell which was enlightening.

Yes I know icestorm toolchain and played a bit with it. But lattice fpga board are either expensive (icoboard) or unobtainium/difficult to source, that’s a shame.

I’ve got a mystorm from the Hack a Day Unconference but I’m struggling to learn Verilog , perhaps is the inconsistency of the documentation and the example around the blackice project…

Then try spinalHDL? they have a risc-v cpu implementation on lattice fpga (with icestorm), so porting it to your mystorm board is a good start.

The Manchester Baby (which predated EDSAC) could do subroutines too ;-) !

ADDR Instruction

0 20 ;Baby starts at addr 1, so this is skipped.

1 LDN 30 ;load negative return address in address 30

2 STO 21

3 JMP 8 ;call indirect subroutine

4 LDN 31 ;load negative return address in address 31.

5 STO 21

6 JMP 8 ;call indirect subroutine.

7 HLT

…

20 JMP 21 ;subroutine merely returns.

21 0 ;actually return addr.

30 -3 ;return addr =4.

31 -6 ;return addr =7.

The SSEM only had 32 words of program / data storage, but this 12 word program proves subroutines are possible with it!

http://curation.cs.manchester.ac.uk/computer50/www.computer50.org/mark1/prog98/ssemref.html