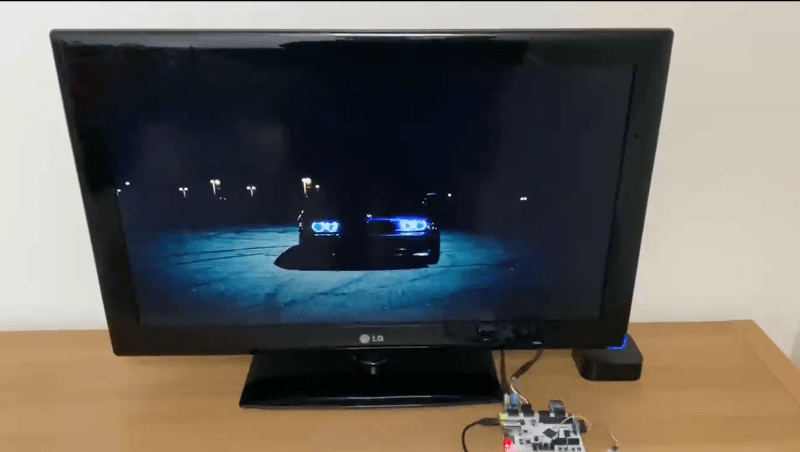

A fact universally known among the Hackaday community is that projects are never truly done. You can always spin another board release to fix a silkscreen mistake, get that extra little boost of performance, or finally spend the time to track down that weird transient bug. Or in [ultraembedded’s] case, take a custom FPGA player from 800 x 600 to 1280 x 720. The hardware used is a Digilent Arty A7 and PMOD boards for I2S2, VGA, and MicroSD. We previously covered this project back when it was first getting started.

Getting from 800 x 600 to 1280 x 720 — 31% more pixels — required implementing a higher performance JPEG decoder that can read in the MPJEG frames, pushing out a pixel every 2.1 clock cycles. The improvements also include a few convenience features such as an IR remote. The number of submodules inside the system is just incredible, with most of them being implemented or tweaked by [ultraembedded] himself.

For the FPGA Verilog, there’s the SD/MMC interface, the JPEG decoder, the audio controller, the DVI framebuffer, a peripheral core, and a custom RISC-V CPU. For the firmware loaded off the SD card, it uses a custom RTOS running an MP3 decoder, a FAT32 interface, an IR decoder, and a UI based on LVGL.

We think this project represents a wonderful culmination of all the different IP cores that [ultraembedded] has produced over the years. All the code for the FPGA media player is available on GitHub.

I think I’ve built myself an HD (720p50) video player out of an #FPGA, #RISCV, #MJPEG and 27,000 lines of Verilog! Going from 800×600 -> 1280×720 just worked with 10 more MHz! I actually plan to sit down and watch a movie on this one evening! https://t.co/4G1ZiN2ipY

– ultraembedded (@ultraembedded) November 21, 2020

That is a really impressive project, and a lot of re-usable HDL blocks, which is always great :D

Thanks! It is very much my key aim to produce re-usable HDL blocks that can have a life outside of whatever project I currently use them in.

I want to see a hardware HEVC encoder that plugs into an ExpressCard slot, or connects by USB C, along with a real USB C ExpressCard.

What USB C specifically do you want to see implemented? USB 3 (.1 .2 5gb 10gb etc etc) or PD? Displayport alt mode? or thunderbolt?