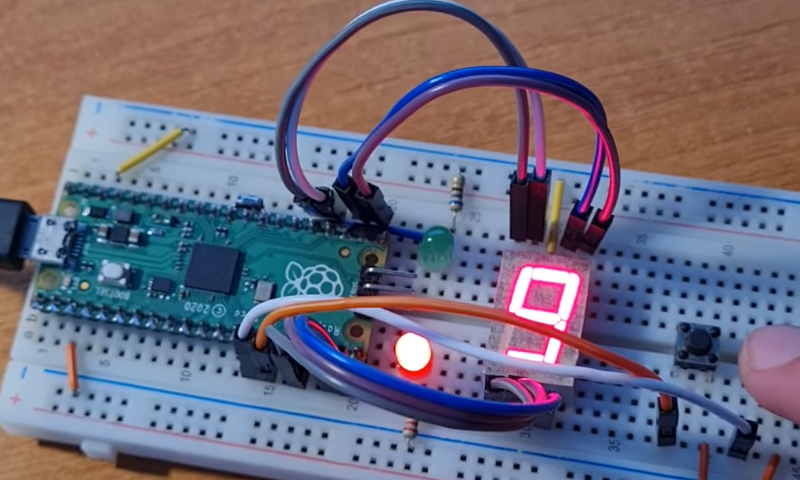

Ever want to play with an FPGA, but don’t have the hardware? Now, if you have one of those ever-abundant Pi Picos, you can start playing with Verilog without getting an FPGA board. The FakePGA project by [tvlad1234], based on the Verilator toolkit, provides you with a way to compile Verilog into C++ for the RP2040. FakePGA even integrates RP2040 GPIOs so that they work as digital pins for the simulated GPIOs, making it a significant step up from computer-aided FPGA code simulation

[tvlad1234] provides instructions for setting this up with Linux – Windows, though untested, could theoretically run this through WSL. Maximum clock speed is 5KHz – not much, but way better than not having any hardware to test with. Everything you’d want is in the GitHub repo – setup instructions, Verilog code requirements, and a few configuration caveats to keep in mind.

We cover a lot of projects where FPGAs are used to emulate hardware of various kinds, from ISA cards to an entire Game Boy. CPU emulation on FPGAs is basically the norm — it’s just something easy to do with the kind of power that an FPGA provides. Having emulation in the opposite direction is unusual, though, we’ve seen FPGAs being emulated with FPGAs, so perhaps it was inevitable after all. Of course, if you have neither a Pico nor an FPGA, there’s always browser based emulators.

We thank [Randy Glenn] for sharing this with us!

>compile Verilog into C++

But then it is not verilog anymore and not even C++. It’s machine code. If a high level language boils only down to mere convenience and experience in using it, you are just limited by the ability of the compiler to interpret and optimize your code to machine code. As obvious as that may sound.

The less steps you take, the better it should be in theory. Unless the compiler is more capable than the user.

Less steps is better but also requires a LOT more effort. This thing is built on top of two other massive projects, verilator and g++/clang.

That obviously heavily depends on the implementation. You can easily build a Verilog compiler that emits much less efficient machine code than a clever Verilog to C++ transpiler used in conjunction with a heavily optimising C++ compiler.

The C++ intermediate step also enables much better hardware support. Nobody wants to reimplement Verilog compiler backends for every microcontroller architecture out there.

Verilog on an actual FPGA isn’t verilog anymore either, it’s a bitstream which sets control bits in various lookup tables and routing muxes. And all digital logic is an abstraction on top of physics, so not sure why one level is more legitimate than another.

Have you bothered reading and understanding the original comment?

With 5kHz maximum clock speed i doubt this is useful for anything pratical, but it is a neat hack. If you want real FPGA look at the open toolchain Yosys/nextpnr. There are (repurposed or made on purpose) dev-boards on the usual websites but it’s more expensive then a Pico, but much faster too…

It is very useful to be able to run the verilog, on “real hardware” (interfacing with say a 7 segment display) to learn the language.

If that’s succesful it will provide a path towards wanting to implement faster stuff on real hardware and spending the $20 – $100 on a “first FPGA dev board”.

Well, i don’t agree totally. Of course you can do some stuff and learn some Verilog, but good luck implementing say a simple UART or dimm an LED using PWM with a 5kHz clock. But still, it certainly has usecases, especially if you want to sneak(?) into FPGA without spending money. A Pico is (was?) cheap and probably already in a lot of drawers of the people reading HaD.

Picos are quite cheap, and widely available. I haven’t yet had problems getting one when I needed it.

Simple UARTs are quite well within a 5 kHz clock’s capability. Sure, you won’t get 115,200 baud or anything, but most of the classical UARTs can’t do that, either.

This isn’t so much intended to be a deployable system. It’s designed to give people a way of wrapping their head around FPGA-style technical paradigms. A good fpga simulator can do that too, but some people have a problem wrapping their heads around a purely-simulated learning environment. This is, after all, why breadboards are so popular relative to circuit emulators, even with all the problems a breadboard can cause.

it would be nice to program the PIO block in hdl since they are a type of very limited CPLD.

a type of compiler from hdl to the PIO assembler languaje

That seems to be exactly what this does, only it takes the intermediate step through C++ to make use of existing compiler work.

Nice for getting practice with FPGA development without needing expensive FPGA dev boards or ghastly proprietary complier toolchains, at a 5KHz clock speed it isn’t good for much mroe than practice though, a normal microcontroller would perform virtually any task faster. What I’d really like to see would be an open-source toolchain for programming actual FPGAs.

You should look at Yosys! https://github.com/YosysHQ

You can get a real FPGA board for $30 with a 200 kGate Spartan 6, and the XSE toolchain is free to use. I cannot see why anyone would spend time avoiding that.

Where? This one is almost $700.

https://www.xilinx.com/products/boards-and-kits/device-family/nav-spartan-6.html

I’m guessing he means something like this

https://m.aliexpress.us/item/3256803558575660.html?pdp_npi=2%40dis%21USD%21US%20%2420.88%21%2421.05%21%21%21%21%21%400b89a67916727744450393771e016a%2112000027018815855%21btf&_t=pvid%3A2ceebf4f-a92d-4eb4-a422-168ca1a6dc5f&afTraceInfo=1005003744890412__msite__c_ppc_item_bridge__xxxxxx__1672774445&spm=a2g0n.ppclist.product.0&gatewayAdapt=gloPc2usaMsite&_randl_shipto=US

I want to experiment with FPGA, but the software to program them is huge, and engineering getto stuff. You sign up, give them all of your personal details. Then download a GB of stuff, install it, fluffing it up even more–and then when you start it, your are greeted with a Java implementation of a Windows 3.11 application.

Again, look at (and even better, support) Yosys! No sign up, no personal details, no spyware phoning home and not too big i think. And it works!

(I am not “affiliated” with this project, just a happy user.)

You don’t even need fpga or simulated fpga first.

You need a simulator and a testbench first, otherwise you will loose days trying to solve trivial issues.

Or, even better, you need an SMT solver and comprehensive annotations for the expected behaviour of your circuit.

Would this not be a perfect platform for Tiny Tapeout projects ?

https://tinytapeout.com/runs/tt02/

Your own ASIC first emulated on the RPI PICO

– and then have it in your hand later for $100 as real ASIC.

The processing speed would be similar…