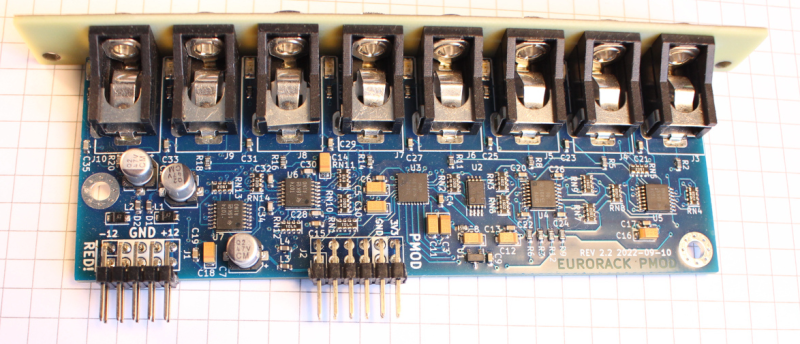

[Sebastian Holzapfel] has designed an audio frontend (eurorack-pmod) for FPGA-based audio applications, which is designed to fit into a standard Eurorack enclosure. The project, released under CERN Open-Hardware License V2, is designed in KiCAD using the AK4619VN four-channel audio codec by Asahi Kasei microdevices. (And guess what folks, there’s plenty of those in stock!)

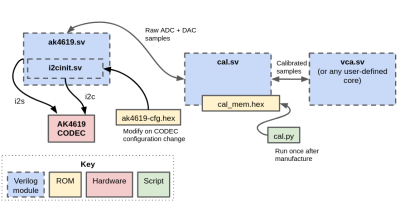

The AK4619 is an audio frontend device, intended for automatic head unit applications, and contains four audio ADCs and four DACs. These enable the eurorack-pmod to handle four incoming and four outgoing channels at the same time. With an I2S or PCM interface, which is hooked up to a PMOD connector on the rear, an external FPGA board of your choice can be connected, of which there is quite some choice. [Sebastian] provides some example code targeted at the iCEBreaker FPGA board which can all be handled by the Yosys toolchain. This deals with the details of the AK4619 codec, as well as a board-level calibration, to allow the user to concentrate on the application code. That might be a pure synthesizer, some kind of DSP audio effect, or something in between. The Verilog code itself is quite straightforward, so should be easily portable to any other FPGA board the user has access to.

Some code for example cores is provided, with a VCO, programmable filter, delay/decimator, and a few other goodies, so plenty of examples to start with for your first FPGA synth project! For learning and simulation purposes [Sebastian] has provided the necessary setups to drive the VCV Rack audio simulator, as well as a handy guide for running Verilog simulation inside VCV.

FPGA audio synthesis is nothing new around here, but new projects in this space are always exciting. As for previous works, here’s one based on an old Xilinx Spartan 6 board, and another for the newer Zynq.

Cool!

More FPGA audio goodness here (not mine)

https://www.youtube.com/channel/UCqQPwJM5BUc2zbbP-_06k2w

Eurorack, check, open source, check. This is great.

Sweet intro to FPGA coding! Audio is just about the right speed to not have to worry too much about FPGA timing, and still make something that’s pretty awesome.

And if you want, you can do it “simulated” in VCV rack? How cool is that?

awesome project! love it. Kudos for releasing it open source – still getting one now ! :)