The Raspberry Pi has been around for over a decade now in various forms, and we’ve become plenty familiar with the Pi Pico in the last three years as well. Still, these devices have a great deal of potential if you know where to look. If you wade beyond the official datasheets, you might even find more than you expected.

Kumar is presently a software engineer with Google, having previously worked for Analog Devices earlier in his career. But more than that, Kumar has been doing a deep dive into maxing out the capabilities of the Raspberry Pi and the Pi Pico, and shared some great findings in an excellent talk at the 2023 Hackaday Supercon.

Under The Hood

Kumar begins by noting that a great many resources went into the creation of this talk. Worthy of note are Jeremy Bentham’s blog, which provided plenty of details on the Raspberry Pi and the workings of the Secondary Memory Interface (SMI). Beyond that, the Pi Pico documentation proved fruitful, as did several logic analyzer projects from out in the wild. Kumar collated this knowledge along with plenty of research, and put together a guide to some of the deeper functionality of the hardware with regards to the concept of a Pi Pico-based logic analyzer capable of running at 100 megasamples per second.

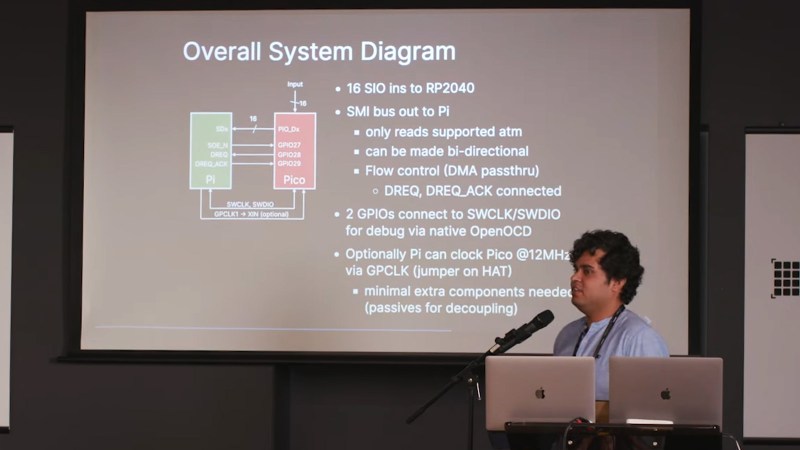

Kumar notes the RP2040 chip at its heart has the useful Programmable I/O (PIO) subsystem, which allows for doing various I/O and data tasks quickly and efficiently. However, the chip is still limited to just 256 KB of RAM and a 1.5 MB/sec max data speed over USB. However, by combining the Pico with a Raspberry Pi 4, Kumar reckons its possible to create a 16 bit, 100 megasample/sec logic analyzer by using the right techniques. For looking at 3.3 V logic, the minimum hardware required would just be a Raspberry Pi and a single RP2040 microcontroller.

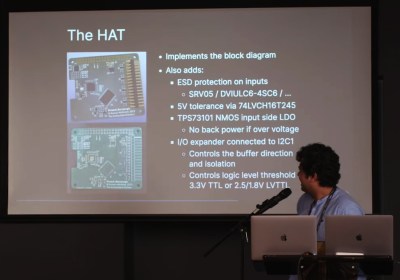

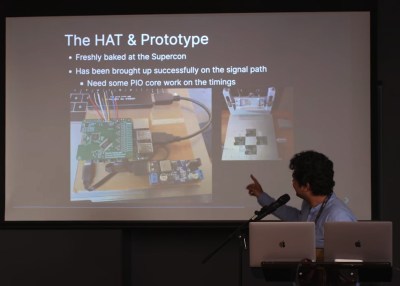

However, a little extra functionality never goes astray. Kumar talks about building a prototype HAT add-on that adds a separate LDO regulator for the RP2040, 5 V tolerant logic buffers, and an I2C input expander to create a pretty useful little logic analyzer. Kumar’s original idea was to use the Pi Pico itself, but there was a problem. With only 26 usable GPIOs, it’s not possible to get 16-bits in and out of the device very easily. Hence, the idea to use the raw RP2040 for direct access to all the necessary pins. However, there was still a problem. The PIO subsystem can only control 30 pins.

To get around this, Kumar noted that the less-flexible SIO subsystem can control all 36 GPIO pins. Kumar found a way to use the dual cores of the Pi Pico to sample the GPIOs via the SIO hardware every clock cycle while remaining in sync. Basically, the SIO hardware samples the inputs, puts the results in RAM, and then the DMA subsystem trucks this over to the PIO. The PIO then handles clocking the data out to the attached Raspberry Pi as required. Combining this technique with overclocking the Pi Pico would help Kumar nail the 100 megasamples/sec target; at the stock clockrate, it wouldn’t be fast enough.

Things only get more complicated from there. Kumar explains issues around bus contention within the Pico, as well as how to clock data into the Pi via the SMI interface. It’s poorly documented, but Jeremy Bentham’s blog was a big help. The talk gets into the nitty gritty here, diving into the precise conditions needed to pipe lots of data out of the RP2040 and into the Pi itself. Meanwhile, the Pi itself gets control over the RP2040 via the SWD pins and GDB debugging with OpenOCD. Everything was then laced together with some code crafted with the aid of ChatGPT.

By the time Supercon rolled around, Kumar was still tangling with some details. The system was passing data from RP2040 to the Raspberry Pi at 41.666 MHz, though there were some aberrations. There was work left to be done on flow control and some other details to get the thing more functional. Kumar also speculated that the Pi 5 might open up new avenues to further improve the project.

Hell yeah

This would be a world easier if RPi would support USB 2.0

which on isn’t 2.0? rp2040 is 2.0 just only full speed

Which is USB 1.1

100% agree. USB 2.0 would make the Pi Pico perfect!

For the record, datasheet at https://www.eevblog.com/forum/projects/state-of-raspberry-pi-adc-support-in-2023/?action=dlattach;attach=1855891

The bottom line appears to be that this has the RPi very much as a master device able to address external devices on the SMI bus, rather than being a slave with registers/FIFOs that an external master can address.

The reason I’ve just done a little bit of digging was because I was wondering whether an RPi could be used to emulate e.g. a USART, before translating the logic into an HDL.