This week, IBM revealed their POWER10 CPU, which may not seem too exciting since it’s primarily aimed at big iron like mainframes and servers. The real news for most is that it is the first processor to be released that is based on the open Power ISA specification v3.1. This new version of the Power ISA adds a number of new instructions as well as the notion of optionality. It updates the v3.0 specification that was released in 2015, right after the founding of the OpenPOWER Foundation.

Currently, a number of open source designs for the Power ISA exists, including MicroWatt (Power v3.0, VHDL) and the similar ChiselWatt (written in Scala-based Chisel). In June of this year, IBM also released the VHDL code for the IBM A2 processor on Github. This is a multi-core capable, 4-way multithreaded 64-bit design, with silicon-implementations running at up to 2.3 GHz and using the Power ISA v2.06 specification.

The ISA specifications and other relevant technical documentation can be obtained from the OpenPOWER website, such as for example the Power ISA v3.0B specification from 2017. The website also lists the current cores and communities around the Power ISA.

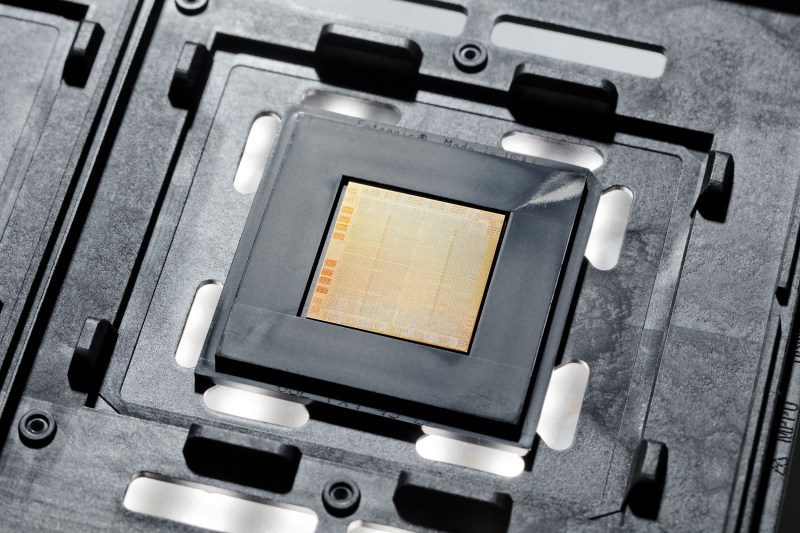

(Main image: POWER10 CPU, credit IBM)

Forgive me for not figuring this out by myself. There are so many projects, and so little Bruce. Why would I be interested in this rather than RISC-V?

A quick search suggests to me that your question might be the opposite way around compared to many in the industry. Power ISA was formalized in 2006, with roots going back to the 1970s while RISC-V was introduced in 2010.

The main difference that I am aware of is that RISC-V is a more “purist” implementation of risc ideas, while Power ISA makes some compromises such as including conditional registers in the name of performance.

RISC-V and OpenPower (POWER9, POWER10, etc) fill two different niches: Risc-V targets the low power side of things, directly competing with the likes of ARM in that respect. POWER on the other hand is targeting the high performance/high power computing, where “A few hundred watts” is just another day in the park.

POWER’s big case is in the world of trusted computing at scales where the whole executable chain, down to IPL on the chip, are signed by the user and you’re doing highly precise highly parallel computations on hundreds of gigabytes of data; This has a lot of different applications in cryptography (“I can guarantee that only my code executed this cryptographic function and knew it happened”) and things like CAD, machine learning, web services, and other “big system” things.

RISC-V aims at the complete other side of the spectrum when it comes to horsepower: Yes, you can validate the HDL, but you can also integrate it alongside custom peripherals and build something that fits in a 24QFP and needs 3.3v at 100mA to do a very specific task.

The OpenPower folks are to x64/Itanium what RISC-V is to ARM/Atmel/PIC.

To see the things that are being done with POWER9, check out Raptor Computing Systems, who have built “secure workstations” — systems where every single part of the machine is independently verifiable down to the code executign on them — that run Linux and BSD. Their primary design goal was a desktop workstation that could be proven to not have been tampered with anywhere in transit, from their manufacturing facility to the end customer — an important thing in the realm of privacy and security. Also take a look at the ever interesting “Climbing the Summit”, a talk on building the first OpenPOWER based supercomputers: https://youtu.be/j18lMp6_BaQ

“Their primary design goal was a desktop workstation that could be proven to not have been tampered with anywhere in transit, from their manufacturing facility to the end customer — an important thing in the realm of privacy and security.”

No NSA hardware intercepts.

Look at it like RISC-V belongs more to embedded world, cheap, simple, low power cores, you could in few clicks and few bucks get a “Red pill” with RV32IMAC MCU to play with, and POWER more close to expensive high performance server CPU’s. Something like ARM and x86 if talk about niche.

At the end of the day they are both just an ISA.

One has no legacy baggage, it cherry picked the best out of what has existed already and tries to avoided mistakes made by other ISA’s, the other has a strong history (baggage) but also is not just based on what already exists.

Currently RISC-V is being targeted at the lowest hanging fruit embedded, because the entry price to that market is going to be much much lower. But it could in 2-5+ years potentially be targeted at phones/tablets/notebooks/desktops and 5-10+ years servers. It has a legacy 32-bit ISA (RV32I) which can only directly address 4GiB of RAM and a 64-bit ISA (RV64I) which could directly access up to 16384 PiB (16 EiB ) of RAM.

Seeing educated people say that an ISA is for embedded only, that was clearly designed for far more use cases, I just find crazy.

e.g. The Xuantie 910 (RISC-V RV64GCV), should be produced with the TMSC 12nm FinFET process (2020-09), will features up to sixteen 64-bit cores running at 2.5 GHz.

That does not sound like the target is the embedded market to me.

Don’t know, define embedded:

From the Medium page https://medium.com/syncedreview/alibaba-is-open-sourcing-its-powerful-new-risc-v-processor-for-5g-and-ai-dcb6f4eebbc4

—

Alibaba’s chip subsidiary Pingtouge (平头哥) yesterday introduced its first product, an RISC-V (Reduced Instruction Set Computer) processor. The Xuantie 910 will be used as a core IP to produce high-end edge-based microcontrollers (MCUs), CPUs, and systems-on-chips. It is tailored for 5G, artificial intelligence, and Internet-of-things (IoT). Pingtounge says the processor will be open-sourced in the near future.

—

Embedded is anything from a small microcontroller to autonomous camera’s, mobile phones, machine vision, etc.

– One is a bit bloated and has a few silly design ideas.

– One is poorly designed but can be very simple to implement.

Both are inferior to ARMv8.

ARM8 decided to fully remove all compressed instructions (no thumb-2).

RISC-V decided that variable-length compressed instruction set was a brilliant idea so they added it as an ISA base extention (That letter “C” you usually see in processor names (e.g. RV64GCV ) stands for “Standard Extension for Compressed Instructions”)

ARM normally uses: ARM Thumb2

In the land of MIPS it is: microMIPS

PowerPC uses: PowerPC VLE

Why is compressed instructions good for performance, I’ll quote from the “The RISC-V Instruction Set Manual”:

‘Of the commonly used 64-bit ISAs, only PowerPC and microMIPS currently supports a compressed instruction format. It is surprising that the most popular 64-bit ISA for mobile platforms (ARM v8) does not include a compressed instruction format given that static code size and dynamic instruction fetch bandwidth are important metrics. Although static code size is not a major concern in larger systems, instruction fetch bandwidth can be a major bottleneck in servers running commercial workloads, which often have a large instruction working set. Benefiting from 25 years of hindsight, RISC-V was designed to support compressed instructions from the outset, leaving enough opcode space for RVC to be added as a simple extension on top of the base ISA (along with many other extensions). The philosophy of RVC is to reduce code size for embedded applications and to improve performance and energy-efficiency for all applications due to fewer misses in the instruction cache. Waterman shows that RVC fetches 25%-30% fewer instruction bits, which reduces instruction cache misses by 20%-25%, or roughly the same performance impact as doubling the instruction cache size.’

I love ARM, ARM has lots of great innovations.

What RISC-V does not bring is anything new to the table, it just selected the very best bits of everything that has existed up until now.

It doesn’ t make sense.

– Either you have a variable length instruction set (for example multiple of 16bits, like MC68K or IBM 360) and optimise op space to get complex instructions, advanced operations, extensions.

– Or you have fixed length and try to keep room for extensions and some flexibility in addressing modes, accessed registers to reduce instruction count. (such as PowerPC or ARMv8).

“Compressed” instructions works well for slow, small embedded stuff, as old THUMB mode. It is not worth it for ultra-wide high performance superscalar designs. RISC-V expects to use op-fusion with wide decoders. That’s not “25 years of hindsight”.

So you are saying that less less CPU cache is going to have higher performance ?

By using a mixed compressed instruction set, you need to decode it before you execute it. so, your adding clock cycles, in order to save cache size. You’re making a trade, between clock speed vs cache size, larger cache size will increase heat, and put require larger fetches, perhaps their better ways to deal with that, smart cache fetching perhaps. Like AMD does.

it would have been nice to have had an article that actual discussed why this chip might be relevant, and why this may/may not be a significant announcement.

ie a quick summary of the news release, with WHY certain things in it might be significant…

maybe the matrix maths engine, or the shard memory model that goes up to petabytes, etc, and why they would be usefull..

I agree. The headline seemed interesting, but the article didn’t seem to explain much more than the headline. I found myself thinking two things: “Who cares?” and “That’s not a hack.”

Click the “revealed” link and read the IBM press release. Apart from anything else they want to make POWER10 & Red Hat the default choice for Hybrid Cloud. I’m not fully up on this, but it is pushing the upper bounds of computing, and that should be of interest to anyone here. It’s certainly interesting to me, and I no longer do much hacking.

I learned more from the comments than from the article! :-D

Hope POWER10 release will drop the prices for POWER9 CPU’s and boards, making them affordable replacement for x86 desktops. For now, 4-core POWER9 + Talos II Lite board will cost you $2000. Still too expensive to play with for average hackaday reader. If the price for motherboard + CPU drops to, say, at least $1000, POWER could break into masses of linux users.

The photo is taller than the entirety of the text. :/

You from ARM marketing?

I guess you folks have your pants in a knot, currently :-)

Arguing which ISA is the best is like arguing about tax policy. Sure you can throw out the 10,000 page current tax code and implement a 1 page flat tax. But unless you address the forces that cause the other 9,999 pages to be added over the years, the flat tax will keep piling on exceptions until it too is 10,001 pages complex.

“This week, IBM revealed their POWER10 CPU, which may not seem too exciting since it’s primarily aimed at big iron like mainframes and servers. ”

People who have a server rack at home may get all stimulated.

“optionality” hmmm. Does that mean options are optional? Is it a recursive word?