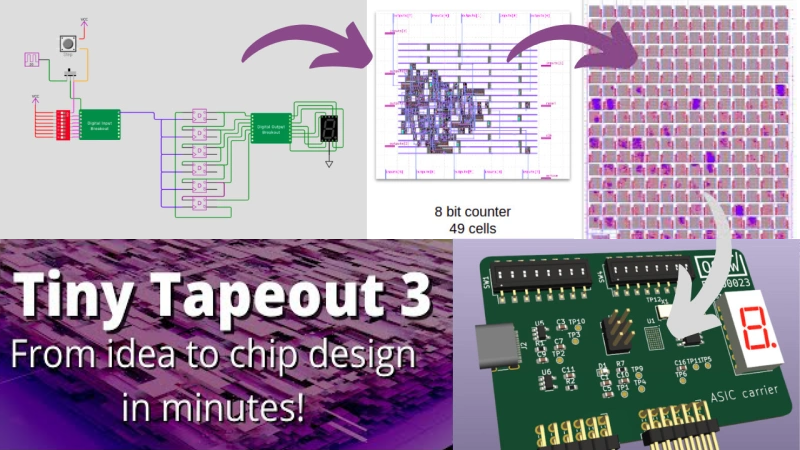

Custom semiconductor chips are generally big projects made by big companies with big budgets. Thanks to Tiny Tapeout, students, hobbyists, or anyone else can quickly get their designs onto an actual fabricated chip. [Matt Venn] has announced the opening of a third round of the Tiny Tapeout project for March 2023.

In 2022, Tiny Tapeout 1 piloted fabrication of user designs onto custom chips referred to as application-specific integrated circuits or ASICs. Following success of the pilot round, Tiny Tapeout 2 became the first paid version delivering guaranteed silicon. For Tiny Tapeout 2, there were 165 submissions. Most submissions were designed using a hardware description language such as Verilog or Amaranth, but ASICs can also be designed in the visual schematic capture tool Wokwi.

Each submitted design must fit within 150 by 170 microns. That footprint can accommodate around one thousand standard cells, which is certainly enough to explore a digital system of real interest. Examples from Tiny Tapeout 2 include digital neurons, FPGAs, and RISC-V processor cores.

Once the 250 designs are submitted, they’ll be combined into a large grid along with a controller. The controller will receive input signals and pump the inputs via a scan chain through the entire grid to each design. The results from each design continue through the scan chain to be output from the grid. Since all 250 designs will be combined on to one chip, each designer will receive everybody else’s design along with their own. This shared process opens a huge opportunity for experimentation.

To get started on your own ASIC design right away, visit Tiny Tapeout. Also check out the talk [Matt] gave at Supercon 2022: Bringing Chip Design to the Masses along with his Zero to ASIC videos. And we’re not saying anything official, but he’ll probably be giving a workshop at Hackaday Berlin.

Did anyone found the electrical specs? What are the voltages and power per pin? Would it be possible to recreate unobtanium ttl chips for restoration purposes?

Io is 3.3v and can drive a few mA. I am going to get an electrical spec sheet together to add to the datasheet.

I’m a bit disappointed that I don’t see which node is used for the designs. The chip size only doesn’t tell much how complex the designs can be.

Skywater 130nm open source pdk

the number of I/O pins is a big limitation.

Yes it is, and the speed. We are working on a new version that adds 8 bidirectional ios and mostly elliminates the slow sample rate by switching from a serial scan chain to combinational muxes and tristates.

May I suggest you look at my “balanced control binary trees” ? I can get a MUX64 with less efforts than a classic binary tree of MUXes. Contact me or look at https://connect.ed-diamond.com/GNU-Linux-Magazine/glmf-218/quelques-applications-des-arbres-binaires-a-commande-equilibree Don’t let your synth create a humongous system !

We have an implementation already in preparation – you can comment here: https://github.com/TinyTapeout/tt-multiplexer

how make a small chip to soundmodem? simple put data from computer and receive. using 2-3 way to convert signal. ideal for meshtastic or reticullum network or simple rattlegram android program

there were a few musical projects on TT02, take a look here: https://tinytapeout.com/runs/tt02/

What a great idea.

It seems, that the cost of one PCB with own ASIC ( and other designs)

comes at a cost of $100 plus shipment – from where?

And where is the link to order a slot? And pay for it?

I tried a few links but was not lucky yet.

8 INs max, 8 OUTs max.

But,

can I use one of my pins to disable the internal scan logic qhich slows down communication?

order it from the front page of the website. We’re still working out where the boards will be fabbed and delivered from. For TT03, you can’t disable the scan chain, it’s the only way we get data in and out. Future versions will have more pins and combinational muxing for faster IO.