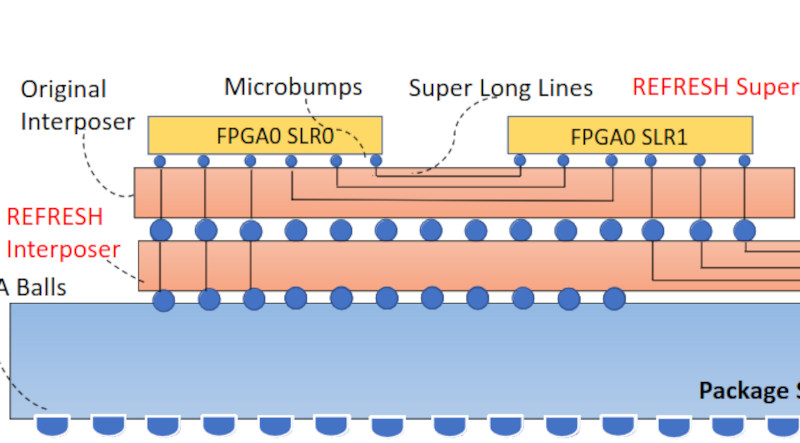

If you really want to look at how much something costs, you need to look at total cost of ownership, not just the sticker price. Same goes for things like pollution and carbon footprint. A vehicle, for example, might have a low carbon footprint in operation but require more carbon in the manufacturing or disposal processes. Researchers have noted that FPGA accelerators get replaced and may wind up as e-waste in as little as two years. They propose REFRESH, an architecture that recycles old FPGAs into new ones by joining multiple FPGA dice with a simple interposer to coordinate the work.

The idea is not as radical as it might first seem. Many modern chips use chiplets anyway, so this is a reasonable extension of that idea. You simply need a way to harvest the old devices.

Of course, design tools for these hybrid recycled FPGAs would require work, too. We imagine that if you are not worried about the carbon footprint, you probably won’t be keen to develop a process for recycling chips, making new ones from them, and standing up a different toolchain. But there are a few factors that could make it worthwhile — tax incentives, for example.

We are more likely to recycle plastic bottles. Or even metal beverage cans.

Heck, I’m pretty sure Xilinx already sells some SKUs which are built this way: A carrier die containing mostly interconnect, the support hardware to configure the interconnect fabric, and the drivers and receivers for external pins. Sitting on top of this is some number between two and four additional dice stacked in a second layer and anchored down to the interconnect fabric below.

The tools are indeed hairy because the timing for nets that stay on one FPGA die is better than the timing for nets that terminate on the carrier (like to an external pin) or nets which cross from one daughter die to another via the carrier .

Virtex-7 2000T was like this, later in UltraScale(Kintex/Virtex) it was common practice.

I wonder if this would actually be more cost effective, compared to either making more of the origional chip, or simply making a newer gen chip.

The material costs of producing a modern advanced chip are a very small part of the total cost; most of the cost comes from engineering. A few pages down this article, there’s an interesting graph (the first one you get to, fig 1)

https://semiengineering.com/what-will-that-chip-cost/

Basically, software, verification, validation, and IP qualification are the vast majority of the cost, with material cost being less than 10%.

This means that recycling a 100$ chip isn’t really saving 100$, you’re saving the 10$ material cost, since the design work is a relatively fixed value. Id be skeptical that harvesting dies out of packaging and rebuilding them into a new chip would be cheaper than simply incorporating that design work (or rather building off of it) into a new next gen chip. Rather than design and qualify a process to reuse old chips, put that design time into building a better new chip.

If you want to lessen the environmental impact of out of date accelerator cards that are fully functional, maybe find applications for the entire card. Maybe release the toolchain for them, so that there’s a 3rd party market?

You may save that $10 material cost but you then need to factor in the cost of collecting the old FPGAs, removing the FPGAs themselves and combining them again. So I would think that this doesn’t actually save money.

Also you need to look at why people discard the FPGAs. They discard them mainly because there are better ones on the market. Even if reusing old FPGAs gets you to the amount of resources you need, chances are they are less efficient, produce more heat and are slower than newer FPGAs, also as someone else mentioned interconnects between FPGAs are slower than connections within an FPGA.

This would likely only be useful for people who aren’t looking for the best or most modern FPGAs, which excludes all the people discarding the FPGAs, but I can see how these reused FPGAs would be useful for less demanding applications even without combining them together.

If you have any old Virtex chips, bundle them with a 5V CPU on a dev board.

Anyone who doesn’t want to worry about voltage logic levels, is a potential buyer.

https://support.xilinx.com/s/question/0D52E00006hpSf9SAE/5v-tolerant-io?language=en_U

I never used such an “FPGA accelerator” before. The link below seems to confirm my first thoughts: A card you plug into a PC and runs custom algorithms to speed up some processes.

https://www.xilinx.com/publications/events/developer-forum/2018-frankfurt/fundamentals-of-fpga-based-acceleration.pdf

So it’s similar (same?) as CUDA https://en.wikipedia.org/wiki/CUDA or some variant of it.

I guess these FPGA accelerators are now at a similar point as PC’s were in the ’90-ies. Back then you started saving for your next PC the day after you bought a new PC, because you knew that in 2 to 3 years time it would be so sluggish, that new software barely ran on it and it’s already time to replace it (or a part of it at least) even though the hardware was working perfectly well. I guess that in the longer term, this stuff gets integrated into the main processor itself. A bit like Xilinx ZYNQ, or combined with a mix of user programmable microcode.

@paulvdh Personally I wouldn’t quite say ‘accelerator’ is the right way to think about it, though they are often used this way. It is more like a ‘blank slate’, not at the software, but the hardware level– And they are reconfigurable, so unlike an ASIC, your design is not ‘fixed’. So, within the constraints/limits of the particular FPGA chip you are working with (i.e. number of logic cells, block RAM, etc), they can basically be, well… Whatever you want them to be. Though we are working at the *gate level*, so the working paradigm can be quite different than programming software, be it bare metal or the OS level. A good, but simple introduction can be found here: https://www.nand2tetris.org/

It really isn’t that similar to CUDA at all. With CUDA you write software to run calculations on your GPU, which has a fixed architecture. With a Field Programmable Gate Array (FPGA) all you start with is a load of resources (look up tables, block RAM, DSP blocks, etc) and then you write in a Hardware Description Language (HDL) which then gets processed into a bitstream that tells the FPGA how it needs to configure itself, basically how all its resources should be connected at a hardware level.

FPGAs are more similar to ASICs than CUDA, in a sense you can think of FPGAs as slower, less efficient ASICs that can be reprogrammed or reconfigured at the hardware level, this makes them much more flexible that ASICs or even GPUs, you can get the hardware set up in the optimal way (at a hardware level) for each set of calculations you need to do.

So FPGAs are not just something that you plug into your PC and run custom algorithms on, you plug it into your PC and then run custom hardware on it.

You can implement pretty much any digital circuit in an FPGA, you can even create CPUs and GPUs within FPGAs. They are also commonly used when testing digital circuits or processors.

I wish people would stop perpetuating the idea that FPGAs are blank hardware. They have lots of dedicated hardware that you are just connecting together. It’s done at startup while cuda and CPU do it when fetching each instruction. You can use FPGA to emulate an ASIC that is created from the same HDL, but they have little in common at the hardware level (similar to compiling C for x86, risc v or arm).

” in 2 to 3 years time it would be so sluggish”

You can thank M$ Windoze for that issue. :)

“2023 is the year of…”

Linux Mint?

As I read it his isn’t “recycling FPGAs” – it is extending the lifetime of existing FPGA designs by making them part of MCM- in essence a “new” FPGA. I don’t see how this is going to extend the service life of an FPGA, it will only extend the manufacturing lifetime of certain die.

I don’t see anywhere that allows for re-use of previously deployed parts- the remanufacturing costs would be significant.

This seems like a more accurate read. Might it be *possible* to recycle old FPGAs with this idea? Sure, but that’s not likely to be cost effective since one would have to remove the chips from all their packaging without damaging them and place them on a new interposer.

Is FP gas like LP gas or is it different? Because we already use a lot of LP gas.

YES

Recycling ANY electronic components would be a good start. Pretty much all of it goes to landfills or is processed in a way that destroys the chips, which is not just wasteful if it’s an FPGA.

To extend the lifespan of existing designs? Sure.

To recycle physical chips already out there? Eh… I mean you can… I’ve certainly wondered… but the issue is that much of the interconnect within the FPGA will be bottlenecked by the number of physical pins, clock domains, physical distance timing and signaling issues. Also power consumption and the need for new designs to handle the external interconnect. The physical size would be larger than true chilplet design as well unless one is talking about batch de-capping and extracting silicon that is literally contaminated….

For clean/old-new stock FPGA IC(s) that can be added to interconnected carrier boards. The cost effectiveness would depend on the state of the market… say another massive chip shortage and this new framework/approach is in practice, then it would allow one to swap out hard to find components and swap in actually available components without needing to perform massive redesign.

I suppose for the hobbyist or for small businesses that are trying out an idea and don’t have significant funding to afford the much larger FGPA(s) then an interconnect board is a great way to build bigger designs without needing to invest heavily in a handful of expensive devices…

But this certainly does zero/nothing for the already in use or deprecated chips already out there.

It is barely cost effective to reball smaller FPGAs,

Bigger ones that are thousands of dollars are effectively recycled nowadays already. You can buy reballed FPGAs and reuse them in your designs. But no one will remove the silicon from the dies.

My friend actually recycled whole video processing FPGA boards for his purposes by mapping the existing connections betwen them using JTAG.

Yeah, I don’t get it. They would need to be really good FPGAs to be used and then discarded so quickly, when better processes allow better FPGAs. If you can stitch a could of old dies together, then why didn’t they just make the die twice the size to start with? FPGAs should be reused and as long as they end up in the recycling chain then they will be.

Instead of recycling your outdated FPGAs, donate me. I can use them.