Monty Python once did a sketch where people tried to summarize Proust in fifteen seconds. Although summarizing eight FPGA-based CPUs is almost as daunting, [jaeblog] does a nice job of giving a quick sketch of how the CPUs work with the Xilinx Vivado toolchain and the Digilent Arty board.

The eight CPUs are: VexRiscv, LEON3, PicoRV32, Neo430, ZPU, Microwatt, S1 Core, and Swerv EH1.

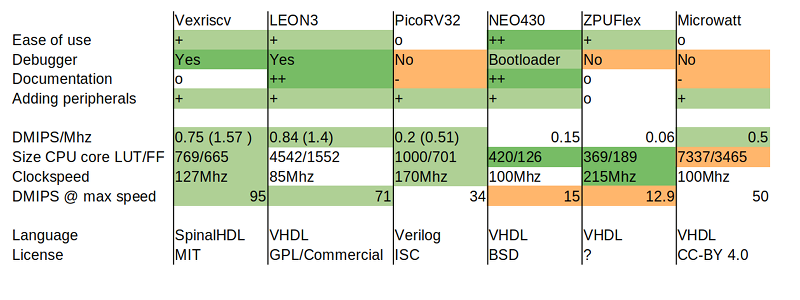

The comparison criteria were very practical: A C compiler (gcc or llvm) for each CPU and no CPUs that were tied to a particular FPGA. Two of the CPUs didn’t fit on the Arty board, so their comparisons are a bit more theoretical. There were other considerations such as speed, documentation, debugging support, and others.

It was interesting to see the various CPUs ranging from some very mature processors to some new kids on the block, and while the evaluations were somewhat subjective, they seemed fair and representative of the things you’d look for yourself. You can also get the test code if you want to try things for yourself.

The winner? The post identifies three CPUs that were probably the top choices, although none were just perfect. Of course, your experience may vary.

If you want an easy introduction to adding things to a soft CPU, this RISC-V project is approachable. Or if you prefer SPARC, check out this project.

My first thought was “You can’t find enough people who have read Proust to have a survey like that.” My take is “Man eats cookie, hilarity ensures.”

Monty Python summarize Proust in fifteen seconds.

Yes, but most Monty Python fans will watch it again, so that’s 30 seconds.

But the second time is completely different.

Thanks for pulling this information together. A row on the table for FPGA resources consumed would be handy also.

Columns for a couple of small commercial soft cores (e.g., ARM, ARC) would provide a useful calibration point.

Or an established reference point like an 8051…

“A row on the table for FPGA resources consumed would be handy also.”

What, like the size of the CPU in LUTs and FFs already on the table? I suppose DSP slices and EBR used for things other than memory would be useful to know. But that is very architecture specific (apples vs kiwi fruit comparisons).

Also be aware that series 7 fabric uses a 6-input / 2-output LUT architecture. Waaay more efficient than a more traditional 4:1 LUT used by many other devices. So comparing series 7 resource usage to other architectures is not simple. There isn’t a rule-of-thumb scale conversion. The relative resource usage from core to code on a 4:1 LUT architecture will have different ratios in the same sort of table comparison (eg. ECP5, etc).

Isn’t that the LUT/FF figures?

I would like to see newer FPGAs, especially smaller ones, come with a small RISC-V microcontroller built in as standard. Makes no sense to waste reprogrammable logic to implement a microcontroller or have a separate microcontroller taking up board space and I/O pins.

I think there is a market for that.. But equally I don’t think its a big enough market to be viable. When its so easy to just bump up the FPGA size or have two seperate IC’s to get both it would take a seriously mass produced product to make that small cpu+fpga on the same IC worth development costs.

Might be a board out there that does need it though, much like those FPGA ‘devboards’ featured here recently that were actually industrial light controllers if memory serves so produced in such large numbers as to be very affordable..

And you already have something very similar with SmartFusion 2 (CM3) and QuickLogic EOS S3 (CM4) on an MCU scale. And of course the ZynQ and Cyclone SoC with Cortex A cores on an MPU scale.

Depends on what you want to do, but what about 65c02 and cc65?

“Proust was a French author most noted for writing A la recherche du temps perdu”

There, I’ve summarized Proust in 15 words and seconds.

I know that’s not what you meant but precision in language matters.

“but precision in language matters”

You’re not going to convince anybody you read Proust with statements like that. ;)

😂😂😂

I’m going to assume the Pythons made enough money that they don’t really care.

Cortex-M3 1.25-1.89 Dmips/MHz. I wrote a wrapper using fusesoc to build for arty. https://github.com/tinylabs/tinylabs-cores

There needs to be a comparison row for Political Correctness. Most of these cores work via the Wishbone Bus which has a Master/Slave architecture – so they must be immediately CANCELLED.

Pity this comparison does not include BOOM and SwerV…

I’ve played around with PicoRV and VexRISC. Vex is faster, but at the expense of complexity. If you want to study a SOC for fun, I like Pico. If you just want something to run code, Vex.

(Just my noob take. Haven’t tried any of the others. Limited experience relative to the OP.)

Stephan Nolting (Author of NEO430) is currently working on another CPU / SoC which is RISC-V compatible! https://github.com/stnolting/neorv32 looks pretty promising!