Early game consoles like the Atari 2600 had a very, very limited amount of RAM. There wasn’t even enough RAM for all the pixels on the screen; instead, pixels were generated by the CPU as they were being drawn. It’s playing with scanlines and colorbusts with code, something we’re now calling. ‘racing the beam’ for some reason.

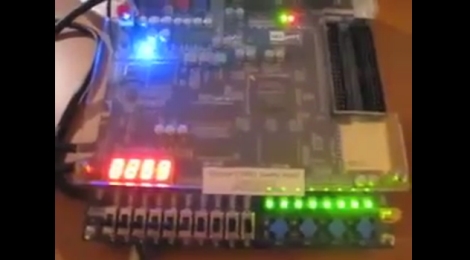

[Sam] is in the middle of an EE degree right now, and for a digital design class he needed to write some Verilog. At the time he was addicted to the game Super Hexagon, and the game mechanics are simple enough for an FPGA. He built his own implementation, but not one with framebuffers. He’s using a pipelined approach where each pixel’s value is calculated just a few clock cycles before it’s displayed. It vastly reduces the memory requirements, on his Altera DE1 board compared to the framebuffer approach.

Video below.