“RISC architecture is going to change everything”, which is why [SHAOS] is building this cool RISC-V DIY retro-style computer.

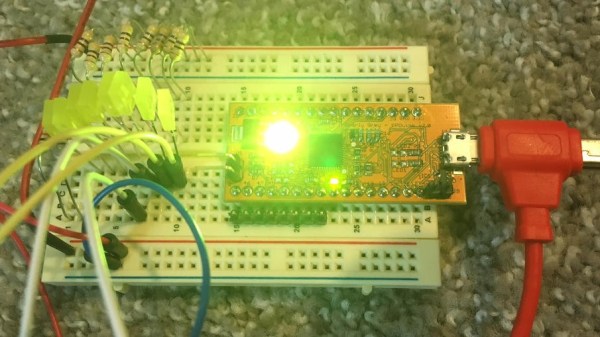

The project took inspiration from another hacker’s work in building a RISC-V emulator; shared in the Hackaday FPGA chat. He took it a bit further and got it going on an UPDuino v2.0 board which features a iCE40 FPGA from Lattice.

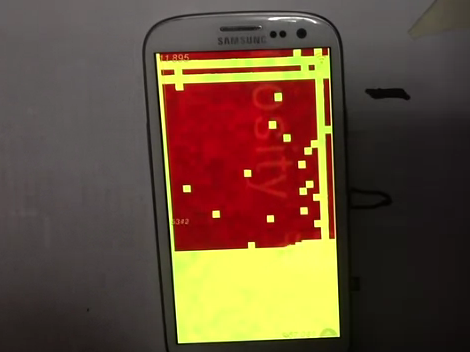

The board passes all the tests for the RISC-V subset he’s aiming for and even run some Zephry RTOS examples. He’s done a really good job of documenting how he got the code to run as well as many of the experiments he’s run so far. All the project files for ICEcube2 software are posted. It’s not the only RISC-V CPU we’ve seen in an FPGA, but the code is actually very clear and worth a read if you’re into such things.

We think anyone interested in duplicating his work could do so somewhat easily and start playing around with this increasingly popular architecture. Or at least get some LED’s blinking in an arcane but meaningful way. Video after the break.