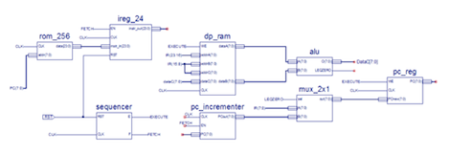

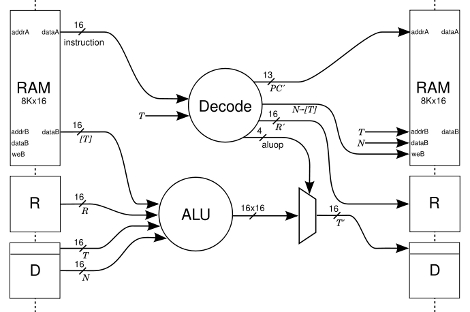

[Hasith] sent in this project where he goes through the process of designing a one instruction CPU in Verilog. It may not win a contest for the coolest build on Hack A Day, but we really do appreciate the “applied nerd” aspect of this build.

With only one instruction, an OISC is a lot simpler than the mess we have to deal with today. There are a few instructions that by themselves are Turing-complete (like Subtract and branch if negative, and Move). Designing an OISC with one of these instructions means it can also emulate a Turing machine.