FPGAs aren’t really programmed, they are configured. Most designers use Verilog or VHDL to describe the desired circuit configuration. Developers typically simulate these configurations before committing them to silicon (a good habit, especially if you ever graduate from FPGAs to ASICs where changes are very expensive). That simulation takes a lot of software you have to install and learn, right?

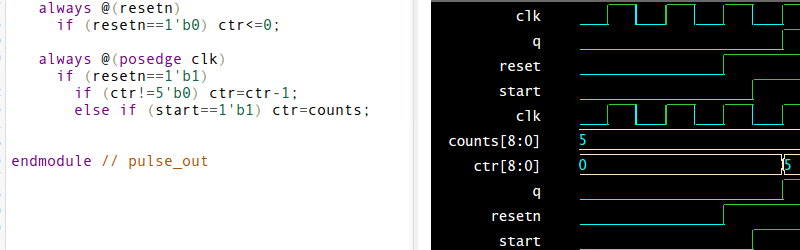

Not necessarily. You can do e-mail, word processing, and PCB layout in your browser. Why not FPGA design? The EDAPlayground website provides two editor views: one for your main “code” and another for the testbench (the simulation driver you use to test your design). You can even open multiple files, if you have a complex design.

Once you’ve entered your Verilog or VHDL (or picked one of many examples) you can run the simulation and see the result right in your browser. No software to install, and–outside of actually learning VHDL or Verilog–not much learning curve.

As [Strauburn], [combinatorylogic], and others commented on our recent post about a VHDL CPU, you can do a lot of learning without ever having your hands on real hardware. The web site gives you access to several different tools (useful if you want to see how your code will behave on different tools) and also many standard verification libraries. There are limited synthesis tools, but honestly, if you want to go to real hardware, you are going to want the vendor tools for the specific FPGA you are using.

As for learning the actual art of FPGA development, a quick search for Verilog tutorial or VHDL tutorial on the web or YouTube will get you started. Verilog is very C-like and VHDL is more like Ada, so choose accordingly. If you are craving VHDL, you can’t go wrong with Free Range Factory’s free book. For Verilog, this list will get you started.

you lost me at “now you log in”

you could ofcourse make a temp google account :P only use it for this :P

also: “We are working on providing additional ways to sign into EDA Playground” so maybe they provide a hackaday.io login? (hint :) )

I wouldn’t be so optimistic.

Not even hackaday.com has hackaday.io login… :)

And it would be usefull to have a way to create a collection of interesting articles that you can acces later.

I agree!

Likewise. Any site that requires gugle or fbuk logins is a none starter for me.

Same here as there really is no technical reason to require one.

Is there an actual reason you avoid any website that requires a login? You can always just easily set any correspondence from them to spam and you’ll never see it again.

Yes. If you aren’t a user to either service, then you have to first create an account there before you can login to the other service.

This is basically online soliciting.

Oh geez. “Online soliciting?” Define that. Do you mean advertising? If you define it as “we know we don’t know security as well as these login providers, so use one of them” then yes, that is online soliciting.

That’s the whole freaking point of this type of login; the site you’re logging into doesn’t need to worry about managing your account or password, or any of that. They rely on the login provider (google or whomever else) to manage that. It’s one more place you can log into, and one less place for hackers to find your credentials.

It’s a way to INCREASE security for the end user. But you haven’t complained enough yet today, so to meet your angst quota you have to attack things that don’t deserve to be attacked.

Ditto: Was outa there.

Me too. Bounced right off the site. I want nothing to do with the children on Goooogle or Faceplant. They say they are “working on other ways to log in”, yeah right. That should take less than an hour – so they really aren’t working on it. Nice idea, poor execution.

For a first touch experience this is awesome!

Especially the XILINX software is a pain if you only want to play a little but have to install a 20GB monster…

Altera’s tools are also a pain and similar in size. Looking forward to trying this web-based simulation. It might beat ModelSim for everyday use on simple designs/individual blocks. I always liked VHDL Simili for simulation, but a few years ago at work, we started having trouble getting licenses from Symphony.

+1 Installing Xilinx toolchain was super-frustrating. I downloaded the installer only to find out that it downloads like an additional 15GB. Then found out the arch I was using needed a different toolchain and had to start all over. Now I have the opinion that all toolschains suck to setup but that one sticks out in my mind as particularly awful.

Haha… same here…

I started the downloads with the single file. There was no warning about the file size so that download died after 2GB because I was downloading it to a FAT32 drive. Most SD / Flash memory sticks will have the same problem as they’re either FAT32 or FAT32ex.

Then I tried the split files install. Something (can’t remember what) went wrong there to so I asked a friend to download the files at his work. They were going to take days for me but only took him minutes.

Now, just don’t get me started on the registration process!!!

I just got an fpga dev board and decided to dive right in! I know c this should be a breeze!

Is what I said before promptly curling up in to a ball and crying after my head exploded

haha I was about to say….then I read your 2nd line and nodded in agreement until I also shed tears of misery.

Lol. Too right. I have a spartan dev board and so far blinky lights are as far as I’ve got. I have the xilinx ide but it’s hard going. The veilog free book mentioned in the post looks useful though. As do similar links in the fgpa post made yesterday.

Yes, it’s not fair at all to compare a code that executes in parallel to a procedural language.

Quote: “Verilog is very C-like and VHDL is more like Ada”

Wrong! Verilog and VHDL may have syntax that ‘looks like’ a programming language but they are NOT anything like a programming language!

Very good article, all the same.

That was my only point: they superficially resemble both of those languages. If you notice the first two sentences are:

FPGAs aren’t really programmed, they are configured. Most designers use Verilog or VHDL to describe the desired circuit configuration.

When I teach FPGA development, I often say that Verilog and VHDL aren’t really programming languages. They are machine readable requirement languages. So just like you write “shall” requirements for human systems engineers, you write requirements in Verilog or VHDL to describe the behavior you want.

But you have to admit that C programmers will be more comfortable with Verilog syntax and VHDL will appeal to the Ada/Pascal crowd even though the internals are quite different.

I am only new to VHDL and I haven’t done Verilog. I just looked up Ada and it’s not much like VHDL to me because it has the dotted OOP structures. Pascal on the other hand, is very close to VHDL’s structure but I doubt many people would remember Pascal.

I briefly tried Verilog and to me Verilog was trying to be a programming language and as a result it was further abstracted away from what is happening at a gate level.

I then switched to VHDL and it is a lot easier for me to relate the code to gates etc.

So at least for me, a history with C or Pascal didn’t really make any difference. I was swayed by the logical expression rather than the structure or syntax.

Hey, what development boards are you using?

If you’re starting our (especially with Xilinx) try a trial copy of the Sigasi editor. Makes life much easier.

I jumped in to the mojo for its cost and supposedly simplified lucid language

Altera has tons of free online video courses covering everything from the fundamentals to some pretty advanced topics:

https://www.altera.com/support/training/curricula.tablet.html#curriculahome

Hey! Free Range VHDL was written by one of my professors at Cal Poly! Glad to see his curriculum getting a shout out here, I loved his class.

Not everything is as simple as Arduino. I’ve used Xilinx Webpack ISE for years-you just have to take the time to learn it. Yes, it is huge-but look at all the chips it has to support and there’s a lot of processing involved in converting your code to a JEDEC file.

The sad thing about is that for the most part, ISE is the best of the worst.

I simulate using Icarus Verilog (IVI). Of course, it’s not much good without a target device, but it works well enough to simulate a design before moving it to a device.

All the IDE’s in my opinion are painful. The worst feature is that they all seem to expect you to create your design *in them*. This is fine for some people, but if you have built a Verilog simulation outside the IDE, getting it into the required directory structure with all the IDE-specific config files is not simple.

Granted I am as likely to use emacs and IVI, but this is nice when I’m at someone’s computer and want to do something quick.

Clearly you haven’t taken any time to learn the IDEs. Vivado in particular lets you not only set the text editor, but also run the necessary scripts from anywhere. You can use Eclipse to edit, synthesize, and implement your design, and use any waveform viewer to see your simulation results. At no point are you ever required to even look at the Vivado GUI.

GTKwave to view the simulation output.

I use GTKWave. I’ve also used Dinotrace (http://www.veripool.org/wiki/dinotrace) which is (if I recall) easier to build from source when you are trying to bootstrap on some machine you can’t install packages on.

For VHDL simulation only, there’s also GHDL at http://gna.org/projects/ghdl. I’ve never tried it (since I need synthesis I tend to stick with the gigantic Xilinx/Altera toolchains), but I heard nice things about it, together with GTKwave to view the waveforms.

There is no reason to require a login just to play with it and the use of modal popup on top of the content is just poor web design.

Isn’t this more of a sandbox for testing code, rather than actually learning fpgas?

In the past, Hackaday mentioned some good sites for actual learning!

http://ureddit.com/class/106959/

http://www.hackshed.co.uk/getting-started-with-cplds-index/

https://learn.digilentinc.com/Documents/238

https://www.youtube.com/user/AntoniusSimplus/videos

https://www.youtube.com/watch?v=yTUuPqJDIN4

Well, you saw I mentioned a few links at the end too (and I like some of yours). However, my point was that getting the environment set up is an inhibitor to learning. With this, you are good to go. Point your browser, log in (not a big deal to me, although apparently some people don’t like that), and either load some canned examples or try your own. And sure, you need a book or a tutorial or something, but it still easier than even finding Icarus and learning how to dump VCDs and display them.

Once you have your sea legs, you can graduate to Icarus or Modelsim or the vendor tools of your choice (which are all a pain to install).

It seems that the comments stopped ABOUT 7 years ago.

Is there any news about this project.

Or have people here tried it recently?

Just tried the links in the post

As for learning the actual art of FPGA development, a quick search for Verilog tutorial or VHDL tutorial on the web or YouTube will get you started. Verilog is very C-like and VHDL is more like Ada, so choose accordingly. If you are craving VHDL, you can’t go wrong with Free Range Factory’s free book. For Verilog, this list will get you started.

Are these links accessible elsewhere??

Free Range VHDL can be found here:

https://github.com/fabriziotappero/Free-Range-VHDL-book

Also check out:

https://icestudio.io – open-source toolchain and visual editor (megabytes instead of gigabytes)

https://www.youtube.com/watch?v=lLg1AgA2Xoo&list=PLEBQazB0HUyT1WmMONxRZn9NmQ_9CIKhb – iCEstick using open-source tools by Shawn Hymel / DigiKey