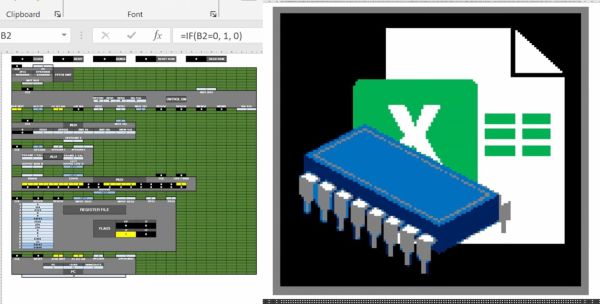

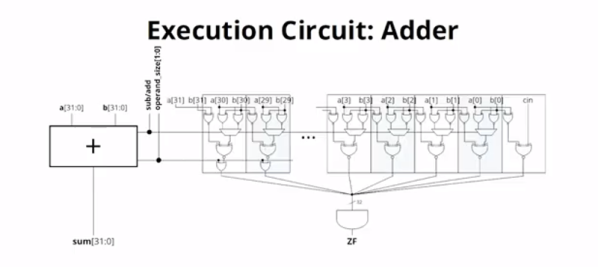

Back in the hazy days of the early home computers, many of us would rejoice at running our first BASIC applications, some of us even built our own 8-bit system from a handful of ICs and felt elated the moment the connected LEDs, screen or other output device would show signs of life. It is this kind of excitement that [Inkbox] has managed to bring to the bane of every office worker: spreadsheet programs like Excel. How, you may ask? Why, by implementing a completely functional 16-bit system with 16 general purpose registers, 128 kB of RAM and a 128×128 pixel color display, all inside an Excel spreadsheet, making it conceivably the world’s first System-on-Spreadsheet (SoS).

Perhaps the most tantalizing aspect of this approach is that it provides a very good visual way to indicate what is happening inside the system using color codes and clearly segregated and marked functional elements. Not only can it be programmed manually, but [Inkbox] also created an assembler for the CPU’s ISA – called Excel-ASM16 – all of which is available from the ExcelCPU GitHub project page. The ASM is assembled into a ROM.xlsx file that can then be run by the CPU.xlsx file by triggering the Read ROM button. After this you are confronted with the realization that although it all works, it’s also incredibly slow, at about 2-3 Hz.

Still, with all the elegance of an IMSAI 8080 front panel, we cannot help but give full points for this achievement. Plus it gives many of us something to do during those exceedingly dull meetings where only serious applications like office suites are allowed.

Continue reading “How To Build Your Own 16-Bit System-on-Spreadsheet”