A couple years back we covered a very impressive transistor logic clock which was laid out so an observer could watch all of the counters doing their thing, complete with gratuitous blinkenlights. It had 777 transistors on 41 perfboards, and exactly zero crystals: the clock signal was extracted from the mains frequency of 50 Hz. It was obviously a labor of love and certainly looked impressive, but it wasn’t exactly the most practical timepiece we’d ever seen.

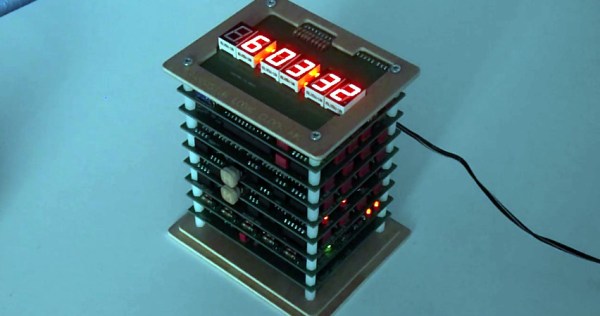

Creator [B Brett] recently wrote in to share news that the second version of his transistor logic clock has been completed, and we can confidently say it’s a triumph. He’s dropped the 41 perfboards in favor of 9 professionally fabricated PCBs, which this time around are stacked vertically to make it a bit more desktop friendly. The end goal of a transistor logic clock that you can take apart to study is the same, but this “MkII” as he calls it is a far more refined version of the concept.

Creator [B Brett] recently wrote in to share news that the second version of his transistor logic clock has been completed, and we can confidently say it’s a triumph. He’s dropped the 41 perfboards in favor of 9 professionally fabricated PCBs, which this time around are stacked vertically to make it a bit more desktop friendly. The end goal of a transistor logic clock that you can take apart to study is the same, but this “MkII” as he calls it is a far more refined version of the concept.

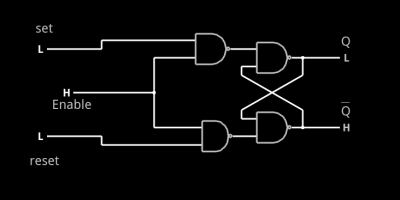

In addition to using fewer boards, the new MkII design cuts the logic down to only 283 transistors. This is thanks in part to the fact that he allowed himself the luxury of including an oscillator this time. The clock uses a standard watch crystal at 32.768 KHz, the output of which is converted into a square wave through a Schmitt trigger. This is then fed into a divider higher up the stack which uses flip flops to produce 1Hz and 2Hz signals for use throughout the rest of the clock.

In addition to the original version of this project, we’ve also seen a beautiful single-board wall mounted version, and even a “dead bug” style one built from scraps.