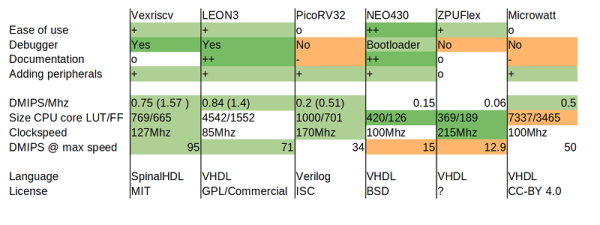

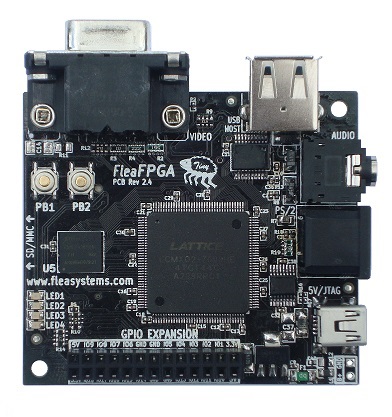

Soft cores for FPGAs come in many different flavors, covering a wide range of applications. The Bit-Serial CPU (bcpu) soft core presented by [Richard James Howe] is interesting for taking up just about the most minimal amount of resources (23 slices, 76 LUTs) while providing the means to run a Forth-based (eForth dialect) interpreter. To this CPU core a UART can be added (92 LUTs), as well as other peripherals.

As [Richard] states, the entire core with UART fits in 73 slices (220 LUTs) on a Spartan 6, while requiring a single port BRAM (block RAM). It features a 16-bit accumulator and lacks features such as interrupts, byte addressability and function calls, but those are not required to run the eForth interpreter. The main purpose of this soft core (other than the challenge) is to have a UART-programmable core that can be slotted in any FPGA design. For more serious requirements [Richard] also has the H2 SoC, which can run full-fat FORTH.

Continue reading “Bit-Serial CPU: Ultra-Tiny VHDL-Based CPU With Forth Interpreter”