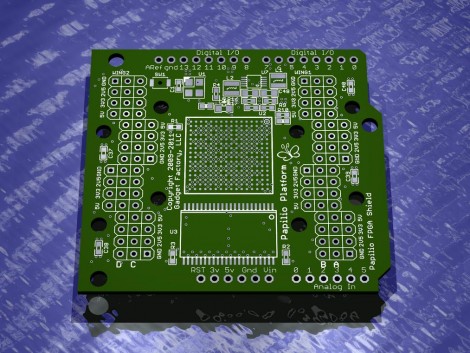

[ Jack Gassett] is working on an FPGA shield for the Arduino. At first the idea of this expansion board seemed a little silly. But [Jack] mentions that the FPGA board can be quite useful for adding higher-order electronic complexity like HDMI capabilities to an Arduino. We’re not totally sold on the idea, but he’s not making the board solely for use with an Arduino either.

The plan is to use a Xilinx Spartan 3A FPGA which comes in a ball-grid array package. And that is the reason [Jack] decided to use Kickstarter for this project. He shared some of his issues with BGA components in a home manufacturing process a while back. To get these working reliably you need to have them professionally assembled, and that requires a sizable upfront investment. But as we read through his proposal it struck us that he’s actually using Kickstarter as a preorder system. You can get a base model with just the FPGA soldered on the board for $55. Not bad considering the chip will cost you at least $20 without assembly. Each level up includes a few more components like SRAM or add-on PCBs.

We get a lot of tips pointing to Kickstarter proposals but this is one of the few that seems right on the mark for supporting open and innovative development. Great work [Jack]!

[Thanks Simon]