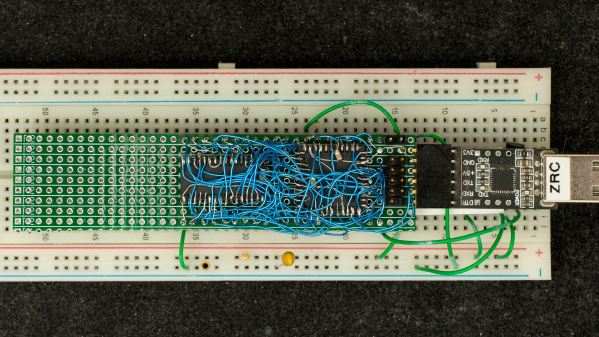

The Motorola 6809, released in 1978, was the follow-up to their 6800 from four years earlier. It’s a powerful little chip with many 16-bit features, although it’s an 8-bit micro at heart. Despite its great improvements over the 6800, and even technical superiority over the Z80 and 6502 (hardware multiply, for example!), it never reached the same levels of success that those chips did. However, there are still some famous systems, such as the TRS-80 Colour Computer, which utilized the chip and are still being hacked on today. [Ted] is clearly a fan of the 6809, as he used a Teensy 4.1 to create a cycle-exact, drop-in 6809 emulator!

A small interposer board rearranges the Teensy pinout to match the 6809, as well as translating voltage levels from 3.3V to 5V. With careful design, the Teensy matches the cycle diagrams in the Motorola datasheet precisely, and so should be able to run any applications written for the chip! A great test was booting Extended Colour BASIC for the TRS-80 CoCo 2 and running some test BASIC programs. Any issues with opcode decoding or timing would certainly be exposed while running an interpreted language like BASIC. After this successful test, it was time to let the Teensy’s ARM Cortex-M7 rip and see what it could do.

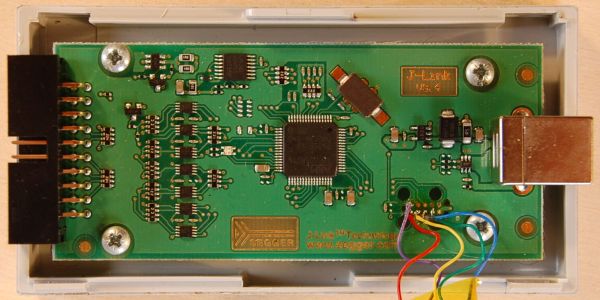

The ORBTrace platform has plenty of untapped potential. There’s

The ORBTrace platform has plenty of untapped potential. There’s