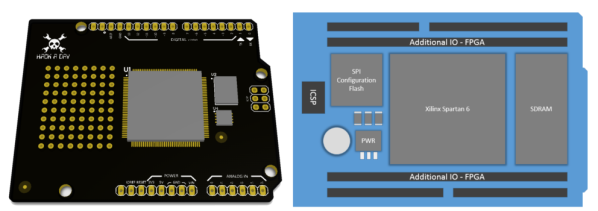

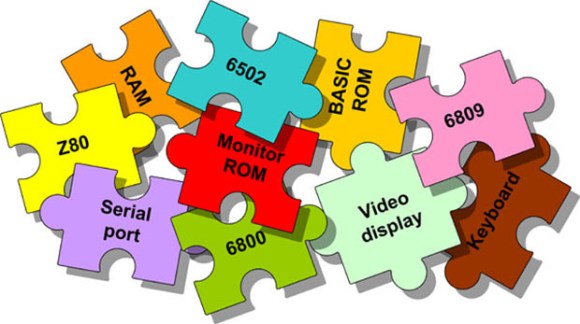

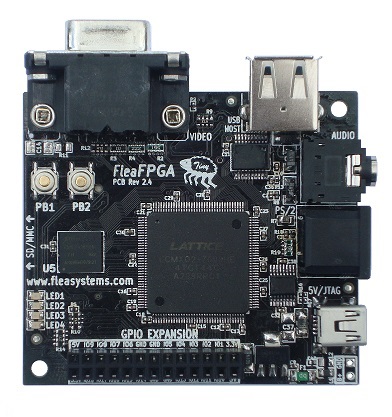

[technolomaniac] is kicking butt over at Hackaday Projects. He’s creating a low cost Arduino based FPGA shield. We’ve seen this pairing before, but never with a bill of materials in the $25 to $30 range. [technolomaniac’s] FPGA of choice is a Xilinx Spartan 6. He’s also including SDRAM, as well as an SPI Flash for configuration. Even though the Spartan 6 LX9 is a relatively small FPGA, it can pack enough punch that the Arduino almost becomes a peripheral. The main interconnect between the two will be the Arduino’s ability to program the Spartan via SPI. Thanks to the shared I/O pins though, the sky is the limit for parallel workflow.

[technolomaniac] spent quite a bit of time on his decoupling schematic. Even on a relatively small FPGA power decoupling is a big issue, especially when high speed signals come into play. Thankfully Xilinx provides guides for this task. We have to mention the two excellent videos [technolomaniac] created to explain his design. Documenting a project doesn’t have to be hours of endless writing. Sometimes it’s just easier to run a screen capture utility and click record. As of this writing, the schematic has just been overhauled, and [technolomaniac] is looking for feedback before he enters the all important layout stage. The design is up on his github repository in Altium format. Due to its high cost, Altium isn’t our first pick for Open Hardware designs. There are free viewers available, but [technolomaniac] makes it simple by putting up his schematic in PDF format (PDF link). Why not head over to projects and help him out?