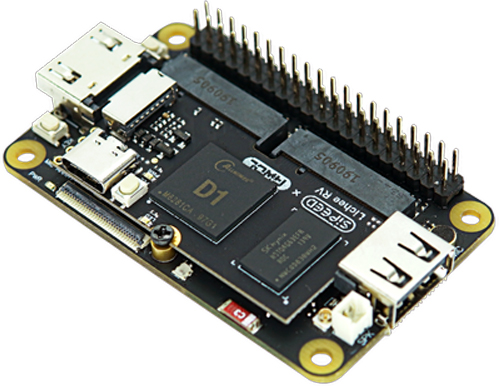

Sipeed have been busy leveraging developments in the RISC-V arena, with an interesting, low-cost module they call the Lichee RV. It is based around the Aliwinner D1 SoC (which contains a Pingtou Xuantie C906 for those following Chinese RISC-V processor development) with support for an optional NAND filesystem. This little board uses a pair of edge connectors, similar to the Raspberry Pi CM3 form factor, except it’s based around a pair M.2 connectors instead. The module has USB-C, an SPI LCD interface, as well as a TF card socket on-board, with the remaining interfaces provided on the big edge connector.

So that brings us onto the next Sipeed board, the Lichee RV Dock which is a tiny development board for the module. This breaks out the HDMI, adds USB, a WiFi/Bluetooth module, audio driver, microphone array interface and even a 40-way GPIO connector. Everything you need to build your own embedded cloud-connected device.

Early adopters beware, though, Linux support is still in the early stages of development, apparently with Debian currently the most usable. We’ve not tested one ourselves yet, but it does look like quite useful for those projects with a small budget and not requiring the power-hungry multi-core performance of a Raspberry Pi or equivalents.

We’ve seen the Sipeed MAix M1 AI Module hosted on a Pi Hat a couple of years ago, as well as a NES emulator running on the Sipeed K210. The future for RISC-V is looking pretty good if you ask us!

Thanks [Maarten] for the tip!