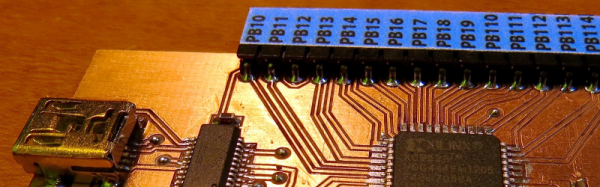

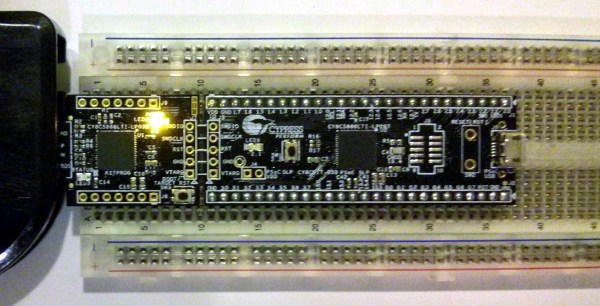

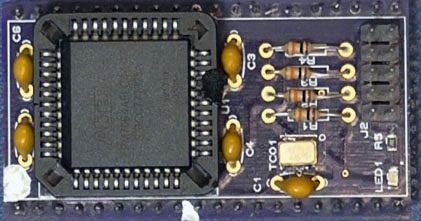

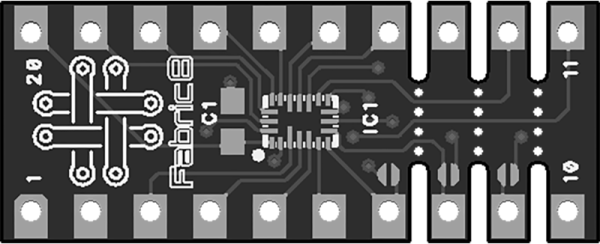

If you read my first post about a simple CPLD do-it-yourself project you may remember that I seriously wiffed when I made the footprint 1” wide, which was a bit too wide for common solderless breadboards. Since then I started over, having fixed the width problem, and ended up with a module that looks decidedly… cuter.

To back up a little bit, a Complex Programmable Logic Device (CPLD) is a cool piece of hardware to have in your repertoire and it can be used to learn logic or a high level design language or replace obsolete functions or chips. But a CPLD needs a little bit of support infrastructure to become usable, and that’s what I’ll be walking you through here. So if you’re interested in learning CPLDs, or just designing boards for them, read on!

Continue reading “A Better Way To Plug A CPLD Into A Breadboard”