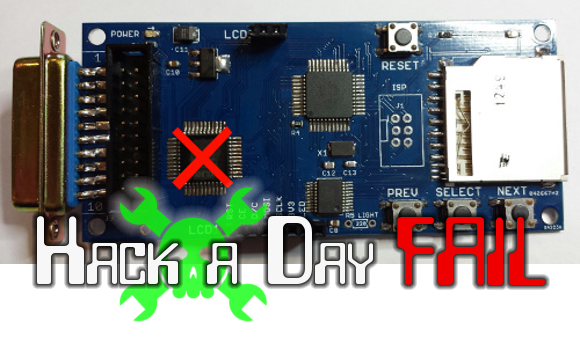

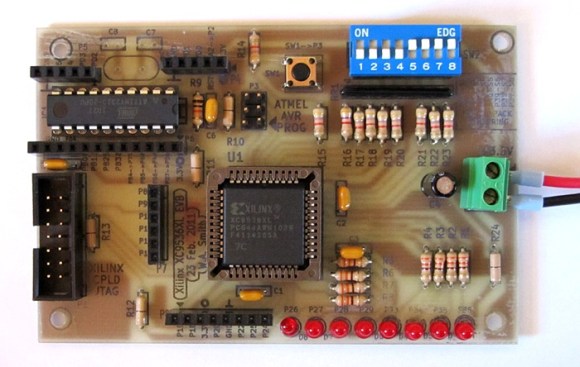

The card you see above is a floppy drive emulator for Macintosh. [Steve Chamberlain] has been hand assembling these and selling them in small runs, but is troubled by about a 4% burn-out rate for the CPLD which has the red ‘X’ on it. He settled into figure out what exactly is leading to this and it’s a real head-scratcher.

He does a very good job of trouble-shooting, starting with a list of all the possible things he thinks could be causing this: defective part, bad PCB, bad uC firmware, damage during assembly, solder short, tolerance issues, over-voltage on the DB connector, or bad VHDL design. He methodically eliminates these, first by swapping out the part and observing the exact same failure (pretty much eliminates assembly, solder short, etc.), then by measuring and scoping around the card.

The fascinating read doesn’t stop with the article. Make sure you work your way through the comments thread. [Steve] thinks he’s eliminated the idea of bad microcontroller code causing damage. He considers putting in-line resistors on the DB connector but we wonder if clamping diodes wouldn’t be a better choice (at least for testing purposes)? This begs the question, why is he observing a higher voltage on those I/O lines during power-up? As always, we want to hear your constructive comments below.

Fail of the Week is a Hackaday column which runs every Wednesday. Help keep the fun rolling by writing about your past failures and sending us a link to the story — or sending in links to fail write ups you find in your Internet travels.

Fail of the Week is a Hackaday column which runs every Wednesday. Help keep the fun rolling by writing about your past failures and sending us a link to the story — or sending in links to fail write ups you find in your Internet travels.