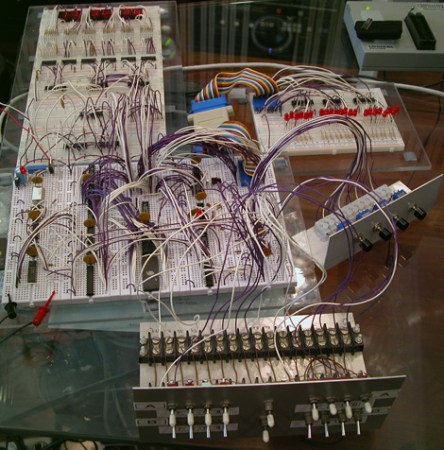

[Peter Bjornx] brings classic microprocessors and modern microcontrollers together with his Arduino bootstrapped 68008 computer. The Motorola 68008 is the 8-bit external bus version of the well-known 68000 (or 68k) microprocessor. A friend gave [Peter] one of these chips, so he built a simple computer around it.

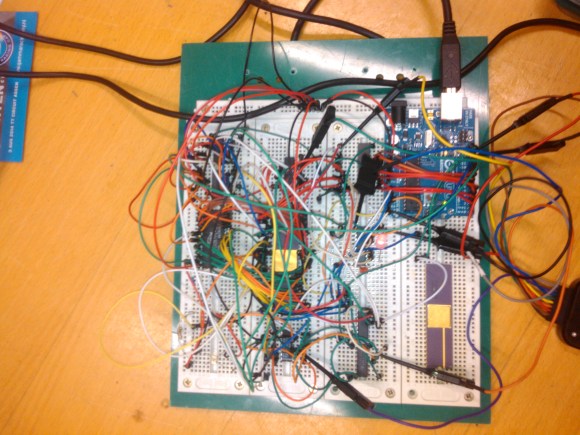

This isn’t one of those clean retrocomputers with every connection carefully planned out and wire wrapped. [Peter’s] created a true hack – a working 68k system on a breadboard created with whatever he had on hand at the time. The real gem of this system is the ROM. [Peter] replaced an EPROM chip with an Arduino.

In the not-so-good-old-days, microprocessors (and many microcontrollers) ran from an external ROM chip. This often was a UV-erasable EPROM. Carefully compiled code was burned into the EPROM with a device programmer. If the code wasn’t perfect, the EPROM had to be pulled and placed under a UV lamp for 20 minutes or so to erase it before it was time to try again. EPROM emulators were available, but they were way too expensive for the hobbyist.

Thankfully those days are far behind us now with the advent of EEPROM and then Flash. [Peter] didn’t want to revisit the past either, so he wrote a simple Arduino sketch which allowed it to act as an EPROM emulator, including address logging via the serial port.

The design still caused [Peter] some headaches, though. His major problem was a classic 68k issue, /DTACK timing. /DTACK or Data Transfer Acknowledge is one of several bus control signals used by the 68k. When the 68k performs a read from the data bus, it waits for /DTACK before it transfers data. The Arduino was too slow to release /DTACK in this case, which caused the 68k to think every read was immediately completed. There is a much clearer explanation of the 68k bus cycles on this Big Mess O Wires page. [Peter’s] solution was simple – a D flip-flop connected to the address strobe took care of the timing issues.

It took quite a bit of tinkering, but the system eventually worked. Peter was able to run the 68008 from its reset vector into a simple loop using the Arduino. It’s only fitting that the 68k program loaded by the Arduino was an LED blinker, everyone’s favorite hardware Hello World.

Thanks [Robert!]