Necklaces aren’t often very high-tech, mostly because of the abuse they have to go through being worn. This was obviously a problem that needed solving, so [Matt Venn] decided to change that by making a necklace out of ASICs just in time for Supercon.

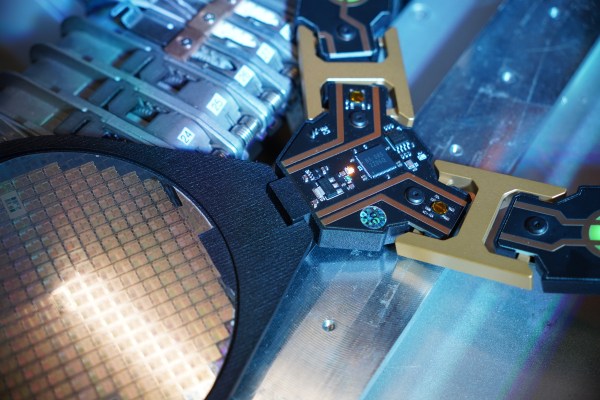

Although this isn’t the first time [Matt] made such a necklace, he though his previous one was “too hip-hop” and not enough “15 million dollar Nikon Lithography Stepper”. Obviously, this means designing the whole chain, art included, from scratch with the blinkenlights to match. Together with [Pat Deegan] and [Adam Zeloof], the team created a beautiful technopunk necklace with art on every chain link and of course a real silicon wafer with a RISC-V tapeout from 2022 on it.

Although this isn’t the first time [Matt] made such a necklace, he though his previous one was “too hip-hop” and not enough “15 million dollar Nikon Lithography Stepper”. Obviously, this means designing the whole chain, art included, from scratch with the blinkenlights to match. Together with [Pat Deegan] and [Adam Zeloof], the team created a beautiful technopunk necklace with art on every chain link and of course a real silicon wafer with a RISC-V tapeout from 2022 on it.

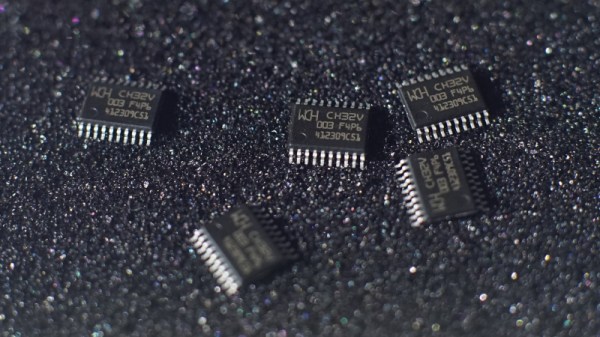

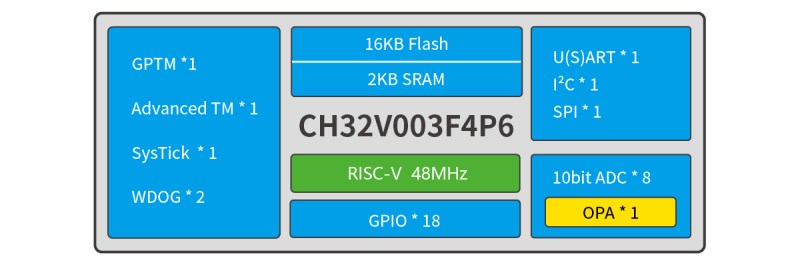

With [Adam] doing modeling for the chain links, and [Pat] and [Matt] designing the electronics required for the mandatory blinkenlights, and some last-minute soldering and assembling the project was finished just in time for Supercon, where it fit right in with all the other blinkenlights. It even runs on one of the RISC-V cores from the same tapeout as the central wafer!