Classic battles: PC vs Mac, Emacs vs Vi, Tastes Great vs Less Filling, and certainly one that we debate around the Hackaday watercooler: command line or IDE? There’s something to be said for using good old command line tools, and even if you like to configure your favorite editor to be nearly an IDE, at least it is one you are familiar with and presumably leverage over several different uses.

Most commercial FPGA tools come with a heavy-weight IDE. The open source tools for Lattice (IceStorm) typically is driven by the command line or a makefile. Until now. [Rochus-Keller] released VerilogCreator which is a plugin for QtCreator.

We were impressed because as IDEs go, QtCreator is both useful and lightweight, two things that don’t go together for many similar tools. [FPGAwars] has had an IDE based on Atom (apio-ide) although it hasn’t been updated in nearly a year. IceStudio sees more updates, of course, but it isn’t so much an IDE as a GUI-based code builder.

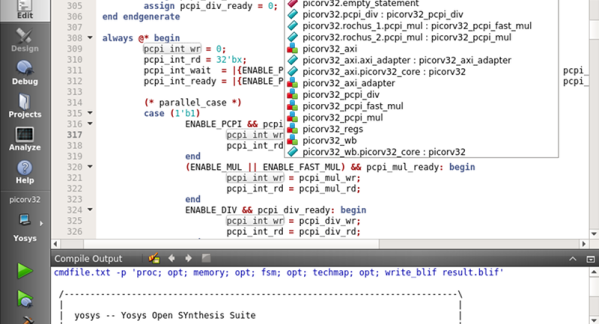

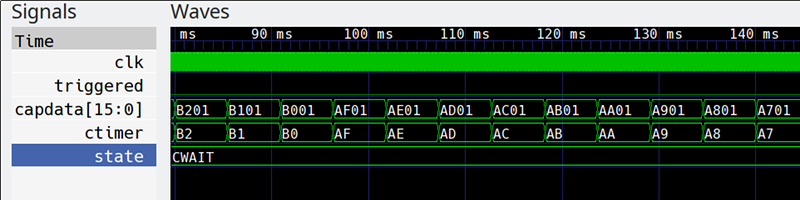

[Rochus-Keller] says there’s more to come. However, even at this early stage the IDE does syntax coloring, tooltips, inline messages, and can analyze source code allowing you to cross-reference symbols as you’d expect. There are configurations for Icarus to do simulations or you can use Verilator or Yosys — the synthesizer behind IceStorm. It appears it can also interact with Tcl-based workflows like those used by most FPGA vendor IDEs.

There’s quite a bit still on the to-do list, so we are excited to see where this is going. QtCreator isn’t hard to learn and it doesn’t’ feel as bloated as some of the big IDEs like Eclipse. If you want a quick introduction to QtCreator, we did that already. If you want to draw boxes instead of writing Verilog directly, try IceStudio.