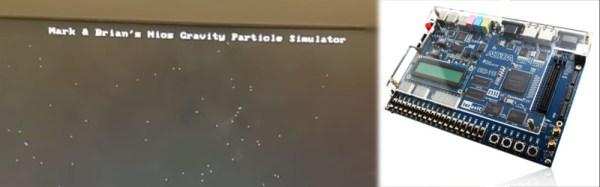

The semester is wrapping up at Cornell, and that means it’s time for the final projects from [Bruce Land]’s lab. Every year we see some very cool projects, and this year is no exception. For their project, [Andre] and [Scott] implemented the audio processing unit (APU) of the Nintendo Entertainment System (NES). This is the classic chiptune sound that regaled a generation with 8-bit sounds that aren’t really eight bits, with the help of a 6502 CPU that isn’t really a 6502 CPU.

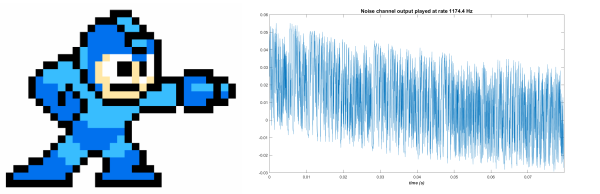

Unlike the contemporaneous MOS 6581 SID, which is basically an analog synthesizer on a chip, the APU in the NES is extraordinarily spartan. There are two pulse wave channels, a triangle wave channel, a random noise channel, and the very rarely used delta modulation channel (DMC) used to play very low quality audio samples. This is a re-implementation of the NES APU for a university lab; it is very understandable that [Andre] and [Scott] didn’t implement the rarely used DMC.

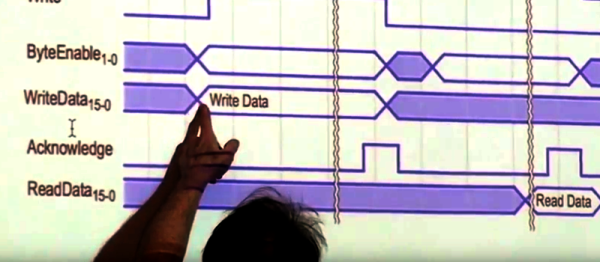

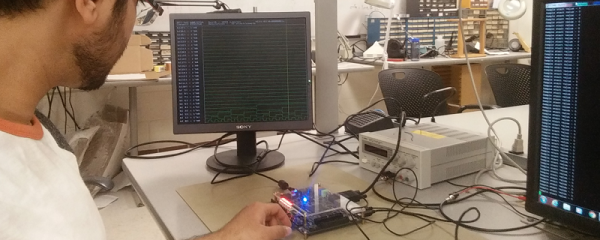

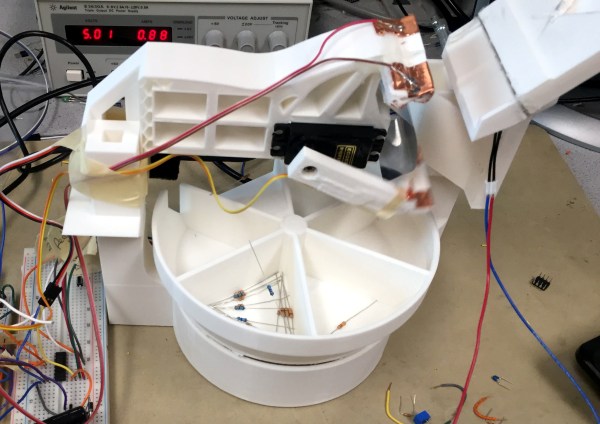

Everything about the circuitry of the NES is well documented, so [Andre] and [Scott] had a great wiki for their research. At the highest level, the APU runs on a 894kHz clock and controls three channels through dedicated registers. These outputs are fed through a mixer, which the guys scaled and combined into a 16-bit output played through a Wolfson WM8731 audio codec.

After implementing the NES APU, [Andre] and [Scott] added an SD card reader that can read the Nintendo Sound Format – the standard distribution format for NES chiptunes – and emulated a 6502 to control the registers. The result is a relatively simple device that plays NES chiptunes with amazing accuracy. The sound files on the project report sound like the real thing, but this is entirely emulated on modern hardware.